1. 서 론

현대 반도체 산업의 주축을 이루고 있는 실리콘 기반 전자소자는 지금까지 그의 성능 향상에 있어 기존 미세 패터닝(patterning) 공정의 개발 및 진보를 통한 집적도 향상을 위한 꾸준한 노력이 진행 되어왔다. 집적도 향 상을 위한 공정기술의 발전과 더불어 포토리소그래피 (photolithography) 기반의 실리콘 반도체 패턴화 방식이 물리적 한계에 도달하게 되어, 기존 실리콘 기반 반도 체 소재 및 소자 공정의 대안을 찾는 연구가 새롭게 연 구되어오고 있다. 그 대표적인 예로서 나노기술(nanotechnology) 은 이러한 전기소자 공정기술의 발전을 위한 핵 심 기술로 평가 받고 있으며, 특히 나노소재(nanomaterials) 또는 나노기반 미세패터닝 공정을 적용한 나노전자소자 (nanoelectric devices)는 기존 실리콘 기반 반도체 소자 의 활성 물질(active material)인 실리콘의 물리적 한계와 기존 공정상의 요소기술 제한 사항을 극복할 수 있다는 가능성을 제시함으로써 그 중요성이 대두되고 있다. 이 미 전 세계적으로 수 많은 연구 그룹에서 다양한 분야 로의 적용에 대한 연구가 활발히 진행되고 있으며, 특 히 메모리 및 센서 소자 분야에서는 향상된 기능을 갖 는 소자에 대한 수요가 늘어남에 따라 더욱 집적화된 디 바이스가 요구되고 있어, 이러한 수요를 충족하기 위하 여 나노스케일(nanoscale)의 전기/전자소자의 개발이 필수 적이다. 앞서 언급한 바와 같이 기존의 실리콘 반도체 공정의 대표적인 미세 패터닝기술인 포토리소그래피 기 술은 특정 파장대의 광원을 사용한다는 것을 특징으로, 패 턴의 미세화를 위해서는 광의 파장이 줄어들어야 하는 데, 그에 따른 포토마스크(photomask)의 재질과 광원의 높은 에너지, 그리고 그에 적합한 감광제(photoresist)의 개발 등의 문제점으로 현재 포토리소그래피 기술을 이 용한 방식은 나노급의 선폭을 구현하는데 있어 공정상 의 한계에 도달해 있고, 이러한 한계를 극복하기 위한 극 단파장대 광원 기반의 공정 설비(Deep UV, EUV, X-ray 등)를 운영하기 위해서는 막대한 투자가 선행되어 야만 한다. 따라서 차세대 나노 반도체 소자 연구 개발 로 손꼽히는 핵심 기술로는, 안정화된 수십~수백 나노미 터 수준의 미세패턴의 구현 및 기존 고가의 반도체 공 정을 대체 할 수 있는 기술을 개발하는 것으로, 현재 다 양한 접근 방법을 통한 차세대 리소그래피(lithography) 기술들이 제안되고 있다.

특히 2003년 ITRS(International Technology Roadmap for Semiconductors)에서 선폭 32 nm 이하의 패턴을 구 현할 수 있는 신기술로서 나노임프린트 리소그래피(nanoimprint lithography, NIL)가 소개 되었다.1) 나노임프린트 공정은 1995년 미국 프린스턴대학 Chou 박사의 연구에 서 최초로 소개되었으며 최대 10 nm 이하의 극 미세 선 폭의 패턴을 구현할 수 있는 기술이다.2-4) 일반적인 나 노임프린트는 기판상에 도포된 레지스트(resist) 고분자 박 막에 나노구조를 갖는 몰드(mold)를 올려준 후 일정한 압력을 가해 몰드의 패턴을 레지스트에 복제, 잔류층 (residual layer) 제거를 위한 방향성 식각 등의 후속 공 정을 포함한 나노 패턴을 형성할 수 있는 미세 패터닝 기법이다. 이는 기존의 광 기반 포토리소그래피와 달리 용액 공정 기반의 단순한 공정이며, 공정을 위한 구성 장비 역시 기존의 공정 장비보다 훨씬 저렴하다는 장점 이 있다. 이러한 나노임프린트 리소그래피는 현재 차세 대 리소그래피 공정으로 각광받고 있으며, 전 세계의 다 양한 연구 그룹에서 선행 연구가 진행되고 매우 다채로 운 결과들이 현재 보고되고 있다.5-10)

기존의 실리콘 기반 반도체 소자의 또 다른 대안으로 서 전기소자의 채널을 구성하는 활성 물질을 실리콘이 아닌 새로운 나노소재로 대체하는 연구 역시 각광 받고 있는데, 그 대표적인 예로서 그래핀(graphene)을 들 수 있다. 그래핀은 2004년 영국 멘체스터대학의 Novoselov 와 Geim 교수 연구그룹에 의해 처음으로 그 물리적 특 성이 확인되었으며,11-14) 탄소 원자 하나의 두께 (약 0.35 nm)를 갖는 이차원 벌집구조(honeycomb structure)의 대 표적인 나노 물질로서 이론적으로 ~200,000 cm2 v−1s−1의 전자이동도와15,16) ~5000 Wm−1K−1의 열 전도도,17) ~1.0 TPa의 영 계수와18) 더불어 물리적, 화학적 안정성을 가 지며 원자 한층 수준의 두께로 인해 가시광 흡수량이 매 우 적어 가시광 영역의 광 투과율이 약 98 %라는 뛰어 난 특성을 띄고 있다.19) 특히, 그래핀의 높은 전자이동 도에 의한 뛰어난 전기 전도도는 대표적인 전극 물질인 구리의 100배에 달하며, 기존 반도체 공정에서 쓰이는 단 결정 실리콘보다 100배 이상 전자를 빠르게 이동시킬 수 있다는 점에서 그래핀은 기존 실리콘 기반 반도체 소자 에서 실리콘을 대체할 활성 물질 또는 기존 금속 전극 을 대체할 전극 물질로 응용이 가능하며, 더 나아가 유 연 투명 전자 소자(flexible, transparent electronic device) 분야의 활용으로 그 놀라운 가능성을 보여준바 있다. 위 에서 열거한 뛰어난 장점에도 불구하고 그래핀은 밴드 갭(band gap)이 없는 독특한 밴드구조에 의해 반도체 소 자로 직접 적용이 용이하지 않았지만, 2007년 전자빔 리 소그래피(electron-beam lithography)를 이용한 나노 패터 닝을 통해 그래핀의 선폭을 줄여 그래핀 나노 리본 구 조가 되었을 때 밴드갭이 형성 및 제어되는 현상이 관 측되었고,20) 이후 수많은 연구 그룹에서 다양한 나노패터 닝 공정을 통한 그래핀 밴드갭 제어(band gap engineering) 에 관한 연구가 시행되고 있다.21-24)

본 연구에서는 나노임프린트 리소그래피 공정을 통해 그래핀 나노리본을 제작하여 최종적으로 그래핀 나노리 본을 채널 활성 물질로 사용한 그래핀 나노리본 트랜지 스터 소자를 구현하는 실험을 실시하여 그 성능을 확인 하였고, 또한 다층으로 형성된 그래핀 필름을 고분자 유 연 기판상에 형성된 박막 실리콘 트랜지스터 소자의 전 극으로 활용하기 위해 직접전사기술을 통한 NMOS-FET 소자를 제작함으로써 우수한 전기 전도도와 유연성을 갖 는 그래핀의 플렉시블 전자소자(flexible electronics)로의 적용 가능성을 확인하였다.

2. 실험 방법

본 연구에서 사용된 그래핀을 합성하기 위해, 먼저 산 화실리콘 기판상에 니켈(Ni) 촉매층을 전자빔증착(e-beam evaporation, Temescal BJD1800)을 통해서 300 nm 두께 로 형성시킨다. 화학기상증착법(chemical vapor deposition, CVD)을 통해서 니켈층 표면상에 그래핀을 형성시키게 되 는데, 증착반응이 일어나기 이전에 약 950 °C의 온도 조 건 하에서 Ar (900 sccm) 과 H2 (700 sccm) 혼합 가스를 반응기 내로 30분 동안 흘려주어 니켈 촉매층의 열적 어 닐링(thermal annealing)을 유도한다. 이후 그래핀 증착을 위해 965 °C의 온도, 750 mTorr의 압력 조건 하에서 Ar (300 sccm), H2 (200 sccm) 그리고 CH4 (10 sccm) 혼합 체를 유입시켜 3분 간 유지한 다음, 반응이 끝나면 반 응로의 급속 냉각(8 °C/sec)을 통해 최종적으로 그래핀을 니켈 촉매층 표면에 형성하게 된다. 이렇게 제작된 그 래핀은 소자 제작을 위해 전사 공정이 따른다. 이를 간 단하게 설명하자면, 니켈 촉매층 기판상 합성된 그래핀 표면상에 톨루엔(toluene) 용매에 용융된 폴리메틸 메타 크릴레이트(Poly methyl methacrylate, PMMA)를 스핀 코팅으로 도포한 후 산화물 습식 식각(buffered oxide etchant, BOE) 용액에 위치시켜 산화 실리콘층을 제거하 여 초순수(DI water) 용액에 옮겨 담는다. 이를 새롭게 준비된 산화 실리콘 기판에 표면장력을 이용하여 전사 (scooping) 해 주게 되면 그래핀/SiO2/Si 기판이 준비된다.

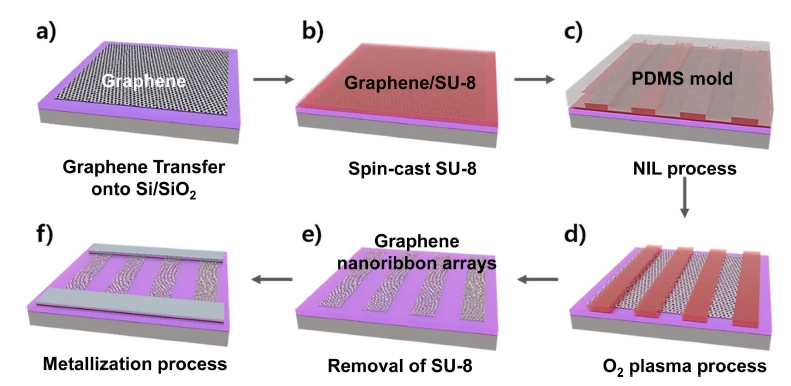

Fig. 1은 그래핀을 활 물질로 사용한 그래핀 나노리본 트랜지스터 소자 공정에 대한 모식도를 나타내고 있으 며, 자세한 내용은 다음과 같다. 탄성체(polydimethylsiloxane, PDMS) 몰드를 이용하여 준비된 그래핀/SiO2/ Si 기판에 SU-8 패턴층을 형성시키기 되는데, 이를 위해 먼저 사이클로펜타논(cyclopentanone)을 용매로 이용하여 8 wt%의 SU-8 고분자 용액을 제조한다. 준비된 SU-8 고 분자 용액을 그래핀/SiO2/Si 기판에 균일하게 도포하고 2000 rpm 의 회전속도로 30초간 스핀 코팅 과정을 진행 한다. 8 wt%의 SU-8 고분자 용액을 실리콘 기판 위에 서 스핀 코팅하게 되는 경우, SU-8 고분자 박막의 두 께는 약 350 nm로 형성된다(Fig. 1(b)). SU-8 고분자 박 막이 형성된 기판은 이후 나노채널이 형성되어 있는 탄 성체 몰드와 완벽하게 접촉하여, 95 °C의 온도에서 3분 간 압력을 가하면서 고화 및 건조시킨다. 기판이 완전 히 냉각 된 후에 탄성체 몰드를 천천히 조심스럽게 박 리시킨다(Fig. 1(c,d)). PDMS/SU-8 고분자를 이용한 나 노임프린트 공정의 장점은 탄성체 몰드와 기판이 직접 접촉하는 영역에서의 충진율이 매우 우수하여 나노채널 내에 식각 보호층(passivation layer)을 형성할 수 있어 공정이 매우 단순하다. 후속공정인 산소 플라즈마(oxygen plasma)를 이용한 식각(etching) 공정에 있어 잔류 SU-8 층은 쉬게 제거가 가능하며 이에 노출 되는 영역의 그 래핀도 함께 제거되므로 패턴의 균일도가 매우 균일할 수 있다. 따라서 나노 임프린트 공정을 통해 SU-8 고분 자 나노 패턴을 제작한 후에 앞서 설명 한 바와 같이 산 소 플라즈마 식각 과정을 통해 노출된 그래핀 층을 제 거하게 되는데, 이때 식각 공정은 15 mTorr의 진공도 하 에서 10 sccm 의 산소 기체를 투입하여 50W의 에너지 로 4분동안 진행한다. 그 결과 노출된 그래핀은 잔여물 없이 완벽하게 제거되고 SU-8 나노패턴 아래의 그래핀 은 제거되지 않기 때문에 그래핀 나노패턴의 형성이 가 능하게 된다. 이후 SU-8 나노 패턴을 용매를 통해 제 거 하는데 이 과정에서 역시 SU-8의 잔여물이 그래핀 표면에 남게 되는 현상이 발견됨에 따라, 잔여 레지스 트의 효율적 제거를 위해서 1000 °C의 온도 조건 하에 서 Ar (900 sccm) 가스를 흘려줌으로써 그래핀 나노 리 본은 유지시킴과 동시에 대부분의 SU-8 잔여물을 제거 하게 된다(Fig. 1(e)). 순수한 그래핀 나노리본 어레이 기 판상 일반 포토리소그래피 및 팔라듐(40 nm)/티타늄(1 nm) (Pd/Ti) 금속화(metallization) 공정을 통해 소스-드레인 전 극을 형성하여 최종적으로 그래핀 나노리본 트랜지스터 가 완성 된다(Fig. 1(f)).

Fig. 1

Schematic illustration of the fabrication process for graphene nanoribbon based FETs through NIL process. (a) CVD grown graphene transfer onto SiO2/Si wafer (b) Spin coating process of SU-8 resist on graphene (c) NIL process to produce nanostructures of line-patterns of SU-8 (d) SU-8 line patterns on graphene which is a result of NIL process (e) After oxygen plasma etching and SU-8 removal process, graphene nanoribbons(GNRs) are formed (f) Metallization to form source/drain electrodes between GNRs-channels.

그래핀을 유연 전극으로 사용한 유연 NMOS TFT 소 자의 제작 과정은 Fig. 5(a)에 도식화 하였고, 자세한 제 조방법은 다음과 같다. 먼저 NMOS 소자의 활성 채널 (active channel)을 구현하기 위해 Silicon-on-insulator 기 판(SOI wafers; 150 mm SOITEC UNIBOUND; 300- nm-thick top silicon layer; resistivity = 13.5-22.5 Ωcm, 1000-nm-thick buried oxide layer)의 p형으로 도핑(doping) 된 상부 실리콘 층(top silicon layer)에 spin-on-glass(SOG, Filmtronic) 용액으로 스핀 코팅 하고 약 700 °C에서 4분 간 급속 열 어닐링(rapid thermal annealing, RTA)을 하여 약 300 nm 두께의 균일한 유리층 필름을 형성 시킨 후, 포토리소그래피를 통해 패터닝 및 습식 식각 공정을 통 해 산화물을 선택적으로 제거한다. 이후 인(phosphorus) 이 포함된 Spin-on-dopant(SOD, Filmtronic)를 스핀 코 팅을 통해 도포하고, 약 950 °C에서 5초간 급속 열 어 닐링하여 노출된 상부 실리콘 층 쪽으로 인 원자가 확 산되어 n형으로 도핑 되도록 한다. 이때, 유리층이 존재 하는 영역은 인 원자가 확산되지 못한다. 이후 습식 식 각 용액(BOE)에 90초 간 위치시켜 SOG와 SOD를 완 벽하게 제거하고 초순수로 세척 한 후 건조하면 NMOS TFT 소자의 활성 채널이 완성된다. 제작된 NMOS TFT 소자의 활성 채널은 불산(Hydrofluoric acid, HF) 처리를 통해 SOI 기판의 매장된 산화실리콘층(buried oxide layer) 을 제거하여 기판과 분리 되는데, 이때 PDMS 스탬프 (stamp)를 제작된 NMOS 소자의 활성 채널 배열(array) 에 부착하여 개별 소자의 위치를 고정한다. 이후 소자 배열이 고정된 PDMS 스탬프를 PI 필름(70 μm thick) 위로 전사(transfer printing)하여 소자 배열이 PDMS 스 탬프로부터 PI 필름으로 옮겨지게 된다. 이때 PI 전구체 (liquid phage, sigma aldrich)를 PI 필름 위에 스핀 코 팅하는데, 이는 전사 인쇄 시 소자 배열이 PI 필름 기 판에 완전히 흡착 될 수 있도록 하는 접착제(adhesive) 역할을 한다. 전사 공정 이후 PI 필름 위에 NMOS 채 널 배열(array)이 고정되면 트랜지스터 소자의 유전층 (dielectric layer)을 형성하기 위해 연속적으로 산화막(i.e., HfO2) 증착이 이루어지고 이후 전극 형태로 패터닝 된 그래핀을 상기의 전사 인쇄 공정과 동일한 방식으로 전 사 하여 소스, 드레인, 탑 게이트(top-gate) 전극을 형성 함으로써 최종적으로 그래핀을 전극으로 한 유연 NMOS TFT 소자가 완성된다. 상기 완성된 소자 두 종류의 소 자들은 반도체 측정기(Semiconductor analyzer, Agilent 4156A)를 통해 소자의 전기적 특성을 평가하였다.

3. 결과 및 고찰

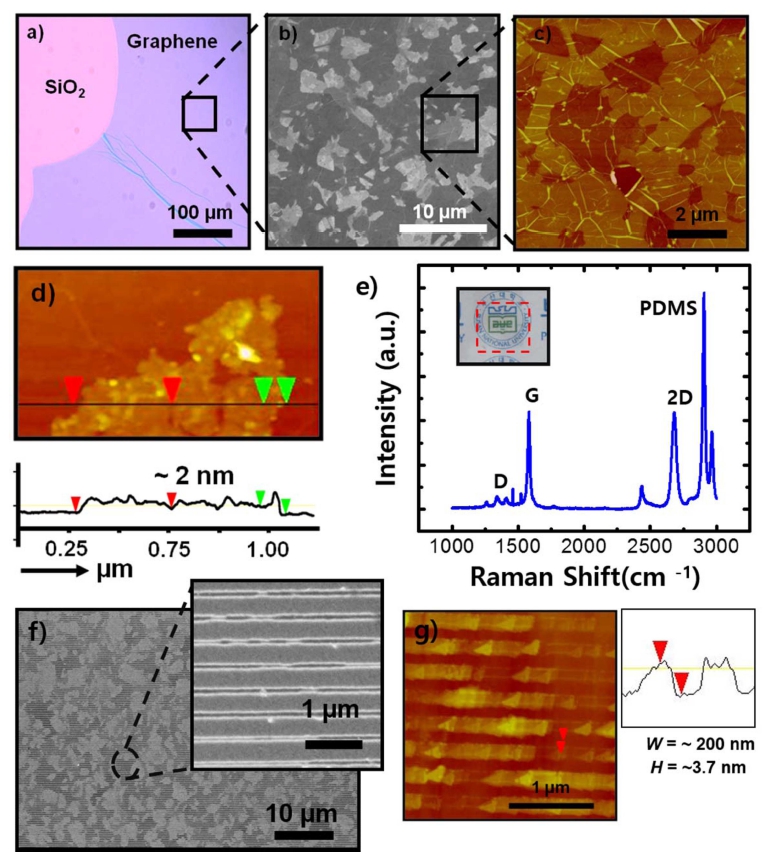

본 연구에서는 화학기상증착(chemical vapor deposition, CVD) 방식을 통해 합성한 그래핀을 각각 채널 물질 또 는 전극 물질로서 적용한 두 종류의 트랜지스터 소자를 제작하였다. Fig. 2는 그래핀을 트랜지스터 활성 채널 물 질로 적용한 그래핀 나노리본 트랜지스터 소자에 대한 표면 측정 결과에 대한 그림으로, Fig. 2(a-c)는 각각 니 켈 촉매 조건에서 화학기상증착법을 통해 성장된 그래 핀을 실리콘 기판(SiO2, 300 nm/Si) 위에 전사한 후 관 찰된 광학현미경 이미지, 주사전자현미경(Scanning electron microscopy, SEM)이미지, 원자힘 현미경(Atomic force microscopy, AFM) 이미지를 나타내며, 표면의 극명한 대 조비(contrast) 차이를 관측할 수 있다. 여기서 같은 밝 기를 가진 부분을 도메인(domain)이라 칭한다. 가장 밝 은 도메인은 단층 그래핀(single layered graphene) 영역 이며 도메인의 밝기가 상대적으로 어두워 질수록 그래 핀 층 수가 증가함이 선행 연구를 통해 보고된 바 있 다.25) 이러한 결과를 통해 합성된 그래핀이 다양한 층수 를 가진 도메인들이 혼합된 구조 임이 증명 되는데, 특 히 선행 연구 결과에서 니켈 상에 합성된 그래핀은 내 재된 도메인들의 평균 층수 및 크기를 니켈 촉매층의 두 께나 화학기상증착 공정 시간을 조절하여 제어할 수 있 음이 보고되었다.25) 또한, Fig. 2(a-c)에서 전체적으로 주 름진 형태를 확인할 수 있는데, Fig. 2(d)는 이러한 그래 핀 표면에 형성된 주름 영역(wrinkled region)에 대한 AFM 관측 결과이며, 측정 결과 약 2 nm의 단차로 주 름이 형성되어 있음을 확인했다. 니켈에서 합성된 그래 핀에 대한 기존 연구에서 화학기상증착 공정을 통한 그 래핀의 성장 중 그래핀과 니켈 촉매 층의 열 팽창 계 수(thermal expansion coefficient)의 차이에 의해 그래핀 시트(graphene sheet)의 두께(약 0.6~2 nm) 범위 내의 작 은 주름이 전형적으로 발생한다는 사실이 보고된 바 있 다.25,26) 특히, 니켈 촉매를 이용해 합성된 그래핀이 가 지는 고유한 주름은 그래핀의 인장 및 수축 응력에 대 한 강도를 향상 시킬 수 있기 때문에 유연/신축 전자 소 자(flexible/stretchable electronics)로의 활용에 있어 장점 이 될 수 있다.

Fig. 2

Morphological analysis of CVD grown graphene transferred to SiO2/Si wafer. (a) Optical microscopy image (b) SEM image (c) AFM image of large-area CVD graphene. (d) AFM image of local area of (c). the arrow represents wrinkled region on the graphene. (e) Raman spectroscopy analysis results of graphene sheet on PDMS elastomer stamp. (f) SEM image of nanoscale SU-8 polymer line patterns (W: ~200 nm) formed on graphene. (g) AFM image of graphene nanoribbons on substrate after oxygen plasma etching and SU-8 removal process. the arrows represent GNR region and SiO2 region respectively in a single line of GNR.

Fig. 2(e)는 라만 분광기(Raman spectroscopy)를 통한 분석 결과를 나타내고 측정을 위하여 532 nm 파장의 레 이저 광원을 사용하였다. 특히 ~1380 cm−1영역에 존재하 는 D 피크(peak)는 합성된 그래핀의 구조상의 결함이나 잔여물에 대한 것으로 측정 결과에서 상대적으로 작은 크기의 D 피크를 통해 합성된 그래핀이 결함이나 잔여 물이 없이 비교적 균일하게 합성 되었음을 알 수 있었 다. 또한, 알려진 바에 의하면, ~1560 cm−1 영역의 G 피 크와 ~2680 cm−1 영역의 2D 피크의 비율(IG : I2D)로 합성 된 그래핀의 층 수를 알 수 있는데, 본 연구에서 합성된 그래핀은 G 피크와 2D 피크의 비가 약 1:1로 대부분의 영역에서 이층 그래핀(bilayer graphene) 또는 다층 그래 핀이 합성되었음을 확인할 수 있었다. 문헌상으로 보고 된 바와 같이 니켈을 기반으로 하는 그래핀은 구리 포 일(foil) 기판상에 합성된 그래핀과는 달리 다층의 그래 핀이 형성되는 것으로 보고되고 있으며,23) 본 연구에서 는 금속 증착에 의한 그래핀 합성 및 전사 공정기술을 개발하고자 하였다. Fig. 2(f,g)는 각각 나노임프린트 리 소그래피 공정 후에 그래핀 기판상 형성된 SU-8 고분 자 패턴에 대한 SEM 이미지와 산소 플라즈마를 이용 한 식각 및 임프린트된 레지스트 패턴 제거 후에 대한 AFM 이미지를 나타낸다. PDMS 탄성체 몰드의 나노패 턴 형상을 따라 나노임프린트 공정기술 제조된 SU-8 고 분자 패턴이 그래핀 기판상으로 매우 균일하게 대면적 으로 형성 되었음을 알 수 있으며, Fig. 2(g)에서 식각 및 고분자 제거를 통해 제작된 그래핀 나노리본(graphene Nanoribbons, GNRs)이 약 200 nm의 선폭으로 형성 되 었음을 확인할 수 있었다. 또한 이 관측결과로 알 수 있 는 점은 초기에 측정된 그래핀의 AFM 이미지(Fig. 2(d)) 와는 다소 상이한 높이의 그래핀 나노리본이 관찰되었 는데, 이는 나노임프린트 공정후 산화 플라즈마 공정에 의해 제거된 고분자 잔류층 제거후 레지스트를 제거하 는 공정에서 고분자의 보호층이 완벽하게 제거되지 않 았음을 나타내고 있으며, 그 층의 두께는 1~2 nm로 초 박막 형태를 갖는 매우 불균일한 모습을 보여 주었다. 이는 최종 트랜지스터 소자의 특성에 영향을 줄 수 있 으므로, 이를 개선하기 위한 공정기술 개발을 현재 다 방면으로 연구 개발 중이다.

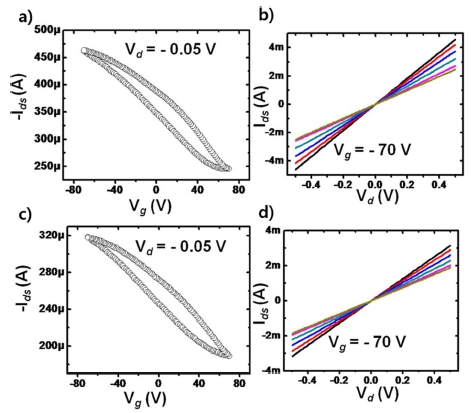

비교실험을 하기 위한 방편으로, 본 연구에서 나노임 프린트공정을 통해 제작된 그래핀 나노리본 트랜지스터 소자를 제작 하기 이전에 성능 비교를 위하여 전형적인 포토리소그래피를 통해 제작된 마이크로 수준의 선폭을 가지는 그래핀을 활성 채널 물질로 사용한 소자를 제작 하여 그 성능을 확인했으며, Fig. 3(a,b)와 Fig. 3(c,d)는 각각 4 μm, 2 μm 의 선폭을 가지는 그래핀 활성 채널 소자에 대한 일정한 소스-드레인 전압(Vds = 50 mV)하에 서 트랜스퍼 특성(transfer characterization) 그래프, 일정 한 게이트 전압(Vg = −70 V)의 변위 내에서의 IV 커브 그래프를 보여주고 있다(Fig. 3(b,d)). 각 소자는 20개의 다채널(multi-channel) 구조로 되어 있었으며, 채널 폭은 8 μm로 유지하였다. Fig. 3(a,c)에서 나태내는 바와 같이 4 μm 선폭 조건에서는 점멸비(on/off ratio)가 약 1.6 이 며 2 μm 선폭 조건에서는 점멸비가 약 1.8으로 미세하 게 증가 했으나 이는 선폭이 줄어듦에 따라 그래핀의 양 자 구속효과가 발생하지 않아 그래핀의 밴드갭의 변화 가 매우 미미한 수준에 머무름에 따라 점멸비가 다소 변 화하게 되나, 소자의 변화를 뚜렷하게 유도하기 위한 나 노급의 구속효과가 일어나지 않았다. 이는 패턴화 된 그 래핀 박막이 반도체적 성질을 띠지 못하고 여전히 금 속에 가까운 성질을 가지고 있기 때문에 낮은 점멸비 와 함께 트랜지스터의 성능이 매우 떨어졌다. Fig. 3(b,d) 에서는 두 선폭 조건 모두 채널 넓이에 선형적으로 전 류값이 증가 했으며, 선폭이 4 μm에서 2 μm로 줄어듦에 따라 전류가 감소함을 확인할 수 있었다. 이는 채널의 개수가 줄어들게 되면, 전류가 흘러갈 수 있는 경로가 더 적어지기 때문에 온-전류(on-current) 값이 줄어들게 되기 때문이며. 같은 맥락으로 선폭이 줄어들게 되면 상 대적으로 전류가 흐를 수 있는 영역이 좁아지게 되어 온 -전류 값이 줄어들게 된다.

Fig. 3

Electrical analysis of Micro patterned graphene field effect transistor (FET). (a) Transfer characterization and (b) IV curves of FET devices consisting graphene micro patterns that have 4 μm width and pitch. (c) Transfer characterization and (d) IV curves of the FET devices consisting graphene micro patterns that have 2 μm width and pitch. All of the electrodes of these devices are made of Pd (40 nm)/ Ti(1 nm). The patterns include pitch which has same size with pattern). Transfer characterization analysis; The drain current (Ids) as a function of gate voltage (Vg: −75 V ~ 75 V) for a source/drain bias (Vds) of −0.05 V is measured on a transistor (L = 8.8 μm, W = 85.6 μm).

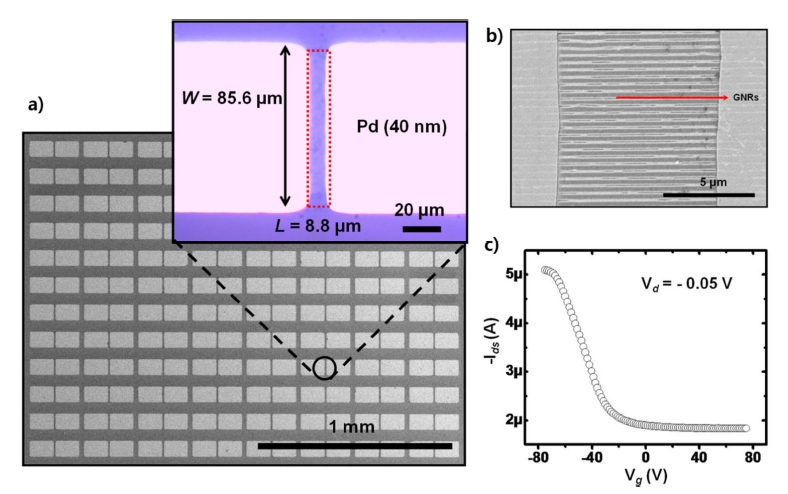

Fig. 4는 앞서 설명한 나노임프린트 리소그래피를 통 해 패턴화된 그래핀 나노리본 기판상에 전통적인 리소 그래피 공정을 이용하여 팔라듐/티타늄 소스-드레인 전극 을 형성, 최종적으로 제작된 그래핀 나노리본 트랜지스 터에 관한 결과로 트랜지스터 구조 및 전기적 특성평가 를 보여준다. 밀리미터 크기를 갖는 대면적의 크기로 제 작된 단일소자 트랜지스터 어레이는 Fig. 4(a,b)에서 보 이는 바와 같이 전극 선폭은 약 85.6 μm, 채널 길이는 8.8 μm로 단일 소자에 약 200 nm 선폭의 그래핀 나노 리본이 약 200개 가량 연결된 다채널(multi-channel) 구 조를 형성하였다. Fig. 4(c) 그래프는 제작된 그래핀 나 노 리본 트랜지스터 소자의 일정한 소스-드레인 전압(Vds = 50mV) 하에서의 트랜스퍼 특성(transfer characterization) 을 나타내며 p형 트랜지스터 특성 및 약 3의 점멸비와 −70 V 게이트 전압 조건 하에서 약 5 μA의 온-전류 값 을 가지고 정상적으로 작동함을 확인하였다. 앞서 Fig. 3의 그래핀 마이크로 크기를 갖는 리본을 이용한 소자 의 결과와 비교하여 점멸비가 약 2배 증가하고, 온-전류 값은 약 100배 감소했음을 알 수 있으며, 이는 그래핀 이 나노 수준의 선폭을 가지게 되었을 때 발생하는 양 자 구속 효과의 결과로 미세한 밴드갭이 생성 되었음을 뒷받침 한다.27) 결론적으로 나노임프린트 리소그래피 공 정을 통하여 p형을 갖는 그래핀 나노리본 트랜지스터를 성공적으로 제조하였으며, 향후 본 연구결과를 토대로 100 nm급 그래핀 나노리본의 미세 선폭 제어 공정기술 개발 및 고분자 잔류층 감소에 의한 고품질의 그래핀 나 노리본 제조를 위한 반응성이 적은 고분자 레지스트의 응용 개발이 필요할 것으로 예상된다.

Fig. 4

Graphene nanoribbons (GNRs) transistors and its electrical properties. (a) SEM image of device array. Inset represents optical microscopy image of single device which includes Pd/Ti contact (W: 85.6 μm, L = 8.8 μm). (b) SEM image of an array of GNRs(w: 200 nm, pitch: 200 nm) (c) Representative characteristic transfer curve of GNR transistor for source/drain bias (Vds) of −0.05 V.

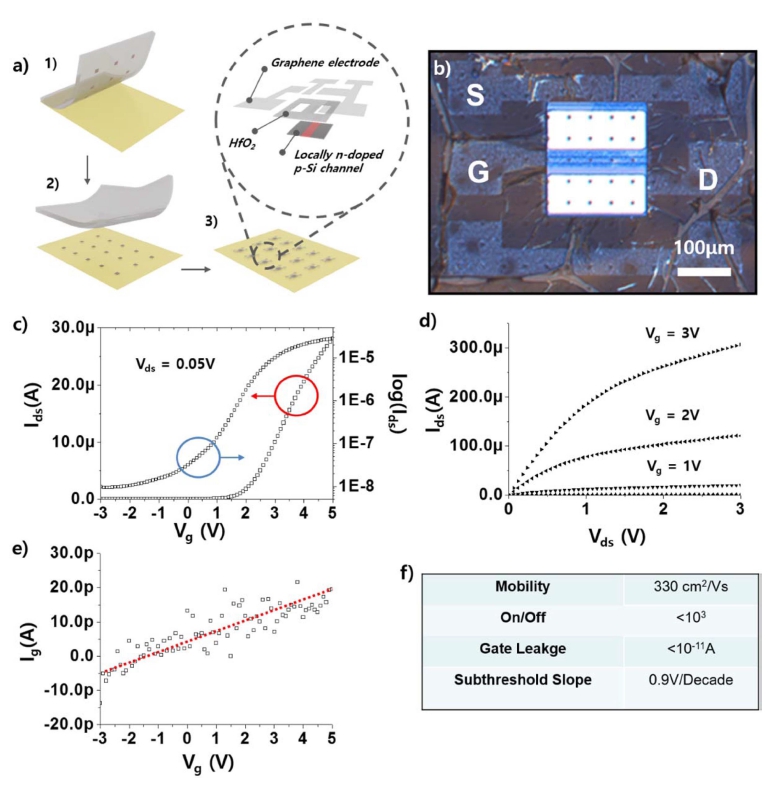

니켈에서 합성된 그래핀은 다층의 그래핀으로 기존의 구리에서 합성된 단일층 그래핀 필름보다는 면저항이 낮 아 전극 특성이 우수한다는 장점이 있다.23,25) 따라서 본 연구에서는 다층으로 합성된 그래핀을 유연 전극으로의 직접 적용을 위한 응용으로 실리콘 소자를 활성물질로 사용하여 응용분야를 확장하였다. 이에 따른 응용 예로 써 그래핀을 실리콘 직접 전극으로 이용한 플렉시블 기 반 n형 실리콘 트랜지스터 소자에 관한 결과를 Fig. 5 에 나타내었다. Fig. 5(a)는 이를 구현하기 위한 전사 공 정에 관한 모식도이며(구체적 내용은 실험방법 참조), Fig. 5(b)는 완성된 소자에 대한 광학 현미경 이미지를 나타 낸다. 광학 현미경 이미지 가운데 위치한 단일 실리콘 소자는 300 nm의 두께로, 폴리이미드(PI) 고분자 유연 기 판상 매우 견고하게 부착된 상태이며 이러한 공정기술 을 통한 유연소자의 직접응용은 많은 연구를 통해 진행 된 바 있다.28) 전통적인 전극으로 현재까지는 금속전극 이 사용되어져 왔으나, 본 연구에서는 기계적 강도가 우 수한 그래핀을 유연 전극을 사용함으로써 플렉시블 포 멧의 소자 적용을 위한 기초 기술을 제공하고자 하며, 실리콘과 그래핀의 우수한 전기적 접합특성을 확인하였 다. 식각 공정에 의해 제공된 실리콘/산화실리콘 기판 및 PDMS 스탬프를 이용한 전사 공정을 통해, 폴리이미드 필름 기판상 전사된 n형 실리콘 마이크로 필름 표면에 마이크로 전극 형태로 패터닝 된 그래핀을 직접 전사함 으로써 초박막 전극을 형성해 주었다.29) Fig. 5(c)에서 보 여지는 그래프는 제작된 소자의 일정한 소스-드레인 전 압(Vds = 50 mV) 하에서의 트랜지스터 특성을 나타내며 게이트 특성 확인을 위해 구동 전압은 −3 V에서 5 V까 지 변화시켜 측정하였다. 높은 유전특성을 갖는 하프늄 산화물의 적용으로 저전압에서의 구동이 가능한 트랜지 스터 성능을 보여주고 있으며, 전형적인 실리콘 소자 특 성인 ~103의 점멸 비를 나타내었다. Fig. 5(d)는 게이트 전압에 따른 소스 드레인 IV 커브이며 서로 다른 게이 트 전압 조건(i.e., Vg = 1, 2, 3 V)에서 소스-드레인 전압 을 0-3 V까지 변화 시켜 측정하였으며, 완만한 출력 저 항(output resistance)을 보여주었다(각각 65.3, 10.4, 4,7 kΩ으로 측정됨). 또한 소자의 안정성을 확인할 수 있는 게이트-소스 간의 누설전류 측정에서는 약 10−11A로 누 설 전류가 매우 미비함을 확인할 수 있었다(Fig. 5(e)). 이로써 그래핀 전극 접촉기술 기반 실리콘 트랜지스터 는 Fig. 5(f)에 정리된 바와 같이, n타입 고성능 트랜지 스터로서 정상 작동 됨을 확인할 수 있었고, 이종접합 헤테로정션 구현이 가능한 실리콘/그래핀 기판 유연 소 자를 구현 가능성을 확인하였다.

Fig. 5

NMOS-TFT device with graphene electrodes. (a) Schematic illustration of the transfer printing method; 1) PDMS elastomer stamp which seize NMOS channel arrays is placed on PI film. 2) After transfer printing, the PDMS stamp is detached from PI film very carefully. 3) After dielectric layer deposition, selective etching provides electrode contact region and transfer-printed graphene electrodes. (b) Optical microscopy image of NMOS-TFT device. (c) Transfer characterization of the device.; The drain current (Ids) as a function of gate voltage (Vg: −3 V ~ 5 V) for a source/drain bias (Vds) of −0.05 V is measured. (d) Output characteristics (Vg: 1 to 3 V from the bottom, 1 V step) (e) Measurement of leakage current between gate and source (or drain) electrode. (f) Summary of performance of NMOS-TFT transistor with graphene electrodes.

4. 결 론

본 연구에서는 PDMS 탄성체 몰드를 이용한 나노 임 프린트 리소그래피 공정을 통해 그래핀 기판 상에 SU- 8 고분자 나노 패턴을 유도하고 건식 식각 공정을 통해 그래핀 나노리본을 형성한 후, 이를 채널 활성 물질로 사 용한 그래핀 나노리본 트랜지스터를 구현하였다. 또한 전 사 기법을 통하여 그래핀을 전극 물질로 활용한 NMOSTFT 소자를 유연 기판 위에서 구현하였으며, 이후 소자 의 전기적 특성을 측정함으로써 그래핀의 트랜지스터 기 능 및 이종접합을 통한 유연 전극으로의 적용 가능성을 확인하였다. 나노 임프린트 리소그래피와 같은 새로운 나 노패터닝 기술은 기존의 반도체 공정의 물리적 한계를 뛰어 넘을 수 있는 잠재력을 지녔으며, 이와 더불어 그 래핀과 같은 새로운 나노소재의 뛰어난 물리적 특성을 접목함으로써 현재 개발중인 반도체 공정연구와 연동된 최적화 연구가 지속적으로 진행된다면, 앞으로의 차세대 반도체 산업을 바꿀 수 있는 새로운 패러다임을 창출할 것으로 기대된다.