1. 서 론

2. TSV 시드층의 기술 동향

3. Seedless TSV 내 금속 충전 기술의 접근 방식

3.1. 첨가제 제어에 의한 TSV 내 Cu 전해도금: seed와 seedless 금속 충전

3.2. 배리어/시드층을 겸하는 Seedless TSV 내 금속 충전 기술

3.3. 금속 나노와이어 및 페이스트를 이용한 seedless TSV 내 금속 충전 기술

3.4. Seedless TSV 내 금속 충전 기술의 한계

4. TSV 내 도금 공정 기술과 하이브리드 본딩법의 연계 가능성

5. 결 론

1. 서 론

실리콘 관통 전극(through-silicon-via, TSV) 패키징 분야가 AI 반도체와 고대역폭 메모리(high bandwidth memory, HBM) 수요 확대에 따라 최근의 시장 전망에서 지속적 성장이 예상된다. 특히 HBM5 이후 세대에서는 메모리 대역폭 요구와 함께 미세 피치 적층 수요가 증가할 것으로 예상되며, 이에 따라 TSV의 전도성 물질의 충전 균일성과 본딩 신뢰성 확보를 위한 연구의 필요성이 커지고 있다.1)

일반적으로 TSV 내부에 접착층, 배리어층, 시드층을 순차적으로 형성한 후 Cu 충전을 진행한다. 시드층은 Cu 충전의 성능을 결정하는 핵심 요소지만, 코팅이 불균일하거나 산화되면, 이에 따른 접촉 저항 증가나 기공 발생 등의 문제를 유발한다.2) Seedless TSV 내 금속 충전 기술은 시드층 형성 과정에서 비롯되는 공정의 복잡성과 비용 문제를 줄일 수 있는 접근법으로, 균일한 금속 충전을 통한 TSV 성능 향상을 목표로 한다.3) Seedless TSV 내 금속 충전 기술은 아직 연구 단계이며 상용화 수준은 초기 단계이지만, 고종횡비 TSV, 3D 패키징, 팬아웃 웨이퍼 레벨 패키징(fan-out wafer-level-package, FOWLP)와 같은 차세대 패키징 분야에서 공정 단순화, 비용 절감, 신뢰성 향상 측면에서 seedless 기술의 적용 가능성이 검토되고 있다. 다만 실제 생산 공정으로 정착하기 위해서는 충전 성능의 확보, 공정 안정성 향상, 장기 신뢰성 보장과 같은 기술적 과제가 여전히 남아 있다.2)

한편, 차세대 집적회로의 미세 피치화와 집적도 증가로 기존 열압착(thermo-compression) 본딩 공정의 한계가 나타나며, 이에 따라 하이브리드 본딩이 새로운 대안으로 주목받는다. 최근 연구에서도 이는 TSV 내 Cu 충전 효율과 공정적 호환성을 동시에 요구하는 새로운 패러다임으로 설명되고 있다. 따라서 TSV 내 충전 기술의 한계와 가능성은 후속 본딩 공정과의 통합적 관점에서 논의될 필요가 있다.4)

본 고에서는 TSV 내 Cu 충전 기술에서 seed 및 seedless TSV의 Cu 충전 기술을 비교 및 분석하고 하이브리드 본딩법과의 연계 가능성에 대해 최근 연구를 조사하였다. TSV 내 금속 충전 기술로는 첨가제 제어 충전, 무전해/전해 합금층 형성, 금속 나노와이어 및 페이스트를 충전재로 이용한 기술 등을 검토하였다. 이를 바탕으로 향후 고집적 반도체 패키징 적용을 위한 연구 방향을 고찰하였다.

2. TSV 시드층의 기술 동향

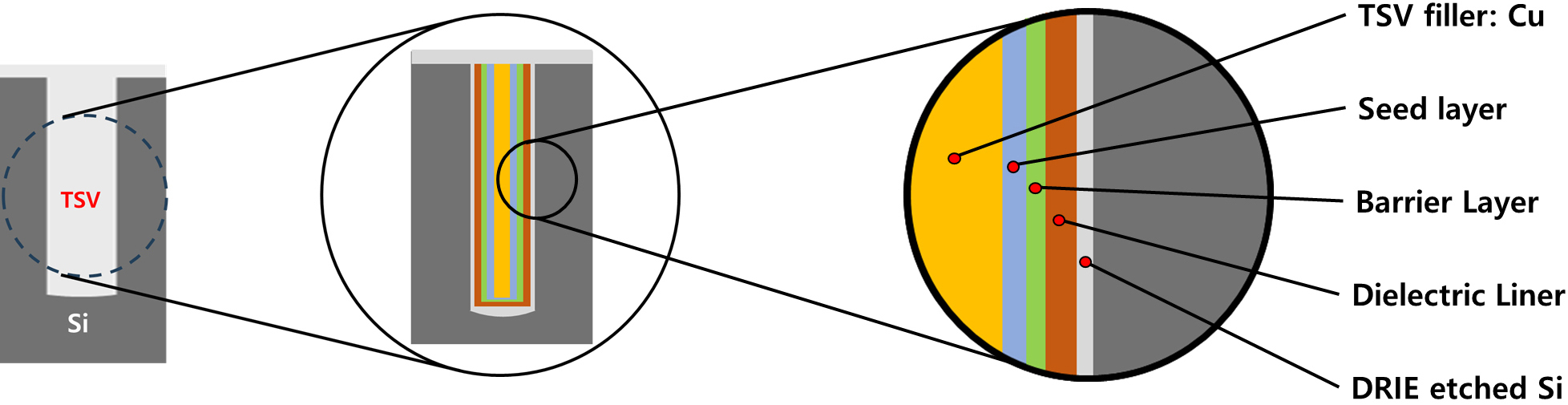

TSV 형성에는 일반적으로 심층 반응성 이온 에칭(deep reactive ion etching, DRIE) 이 사용되며, SF6를 이용한 실리콘 식각과 플루오로카본 측벽 패시베이션(passivation)을 수초 단위로 반복하여 고종횡비 비아를 구현한다.5)Fig. 1은 DRIE을 통해 식각된 실리콘 비아 내부에 형성되는 주요 층 구조를 모식도로 나타낸 것이다. TSV는 절연층, 배리어층, 시드층, 그리고 금속 충전층으로 구성되며, 각 층의 연속성과 균일성이 신뢰성에 직접적인 영향을 미친다. 절연층 위에 증착되는 접착층은 계면 결합력을 높여 기계적 안정성을 확보하며, 배리어층은 Cu의 실리콘 확산을 차단하고 시드층 증착을 위한 젖음성을 제공한다.6)

시드층은 물리적 기상 증착(physical vapor deposition, PVD)이나 원자층 증착(atomic layer deposition, ALD)으로 형성되며, 이후 전해도금을 수행해 비아 내부를 Cu 등의 전도성 물질로 충전한다.7) PVD는 생산성과 비용 효율성이 높지만 단차(scallop) 코팅성이 낮아 TSV 바닥에 30 nm 시드층을 확보하려면 상부에 약 800 nm 이상의 두꺼운 증착이 필요하다. 반면 ALD는 증착 속도가 1 nm/min 이하로 느리지만 우수한 균일 증착이 가능하여 고종횡비 TSV 적용에 유리하다.8)

Li 등2)의 최신 연구에 따르면 PVD가 종횡비 10 수준까지는 산업적으로 널리 사용되지만, 종횡비 15 이상에서는 측벽 시드층의 불충분한 코팅으로 인해 기공이나 seam 등의 충전 결함이 발생한다. 무전해도금(electroless deposition, ELD) 또한 고종횡비 TSV에 대한 적용 가능성이 검토되었으나, 공정 제어와 기체 발생 문제로 인해 연속적인 시드층 형성에는 한계가 있다. 반면 ALD는 초박막을 균일하게 증착할 수 있어 고종횡비 TSV의 시드 형성 대안으로 주목받고 있다. 이들은 직경 약 2.2 µm, 깊이 45 µm (종횡비 > 20)의 TSV 내부에 ALD super conformal Cu 시드층 구현 가능함을 실험적으로 제시하였다. 또한 투과전자현미경(transmission electron microscopy, TEM) 및 주사전자현미경(scanning electron microscopy, SEM) 분석을 통해 Ru 하부층을 조합한 ALD-Ru/ALD-Cu 구조에서는 TSV 내부의 전 영역이 균일하게 충전되어 결함이 관찰되지 않음을 확인하였다. 최근에는 알칼리-산 이중 촉매 ELD-Ni 공정을 통해 70 µm, 깊이 530 µm TSV 내부를 기공 없이 충전하고 안정적인 전기적 특성을 확보한 결과를 확인하였다.8)

Table 1은 TSV 시드층 증착 방법에 따른 생산성과 균일성을 나타낸 것이다. PVD는 대략 500 nm/min의 빠른 증착 속도를 가지고 있으나 단차 피복률이 낮아 고종횡비 구조에는 불리하다. 다만 ALD는 증착 속도는 대략 50 nm/min으로 느리지만 초고종횡비 TSV에서도 균일한 코팅을 확보할 수 있다.9) ELD는 생산성과 균일성이 PVD와 ALD의 중간 수준을 보여 시드층 형성 대체 기술로 적용될 가능성을 보인다. Step coverage는 시드층의 상・하부 두께비 (bottom/top thickness × 100 %) 기준으로 판단하였다.

Table 1.

Comparison of seed layer deposition methods for TSV (through-silicon-via) structures.

| Seed layer | Diameter (µm) | Depth (µm) | Aspect Ratio | Productivity | Step Coverage | References |

| Cu | 20 | 65 | 3.3 | / | / | Wang et al. (2019)10) |

| PVDa)-Cu | 6 | 30 | 5 | 1.42 µm/h | 1.5 % | Wei et al. (2014)11) |

| PVDa)-Cu | 10 | 100 | 10 | / | 9.56 % | Song et al. (2013)12) |

| ALDb)-Ru | 10 | 100 | 10 | 0.216 µm/h | Full coverage (~100 %) | Killge et al. (2019)13) |

| ALDb)-Cu | 2.2 | 45 | 20 | 0.02 µm/h | Full coverage (~100 %) | Li et al. (2025)2) |

| ELDc)-Co | 4.8 | 53 | 11 | 2.9 µm/h | / | Chen et al. (2018)14) |

| ELDc)-Cu | 2 | 30 | 15 | 0.39 µm/h | 30 % | Inoue et al. (2013)15) |

Mori 등16)은 면 선택적 ALD (area-selective ALD)를 이용해 Ru/ZnO 이중층 구조를 제안하였다. Ru는 절연층 및 시드층 역할을, ZnO는 SiO₂ 표면에만 선택적으로 증착되어 Cu 확산을 억제하는 배리어층으로 작용한다. 특히 도데칸티올(dodecanethiol, DDT)을 억제제로 사용해 ZnO의 선택적 증착성을 확보하였으며, 그 결과 Ru 단일층 대비 내열성과 접착력이 크게 향상된 안정적인 다기능층이 구현되었다. 이러한 Ru/ZnO 이중층은 TSV 측벽에만 배리어를 형성하고 비아 바닥은 barrier-free로 유지하는 ‘bottomless barrier’ 개념에 적용될 수 있어, 비아 저항 저감과 고신뢰성 3차원 집적 회로 구현에 기여할 가능성이 있다.

따라서 기존 TSV의 시드층을 구현하기 위한 각 기술은 장단점을 가지며, 특히 고종횡비 구조에서는 PVD의 단차 피복률, ALD의 낮은 증착 속도, ELD의 공정 제어 복잡성이 주요 과제로 남아있다. 이중 촉매 반응 ELD와 Ru/ZnO 이중층과 같은 새로운 접근은 한계를 극복할 가능성을 제시하지만 여전히 장기 신뢰성 확보가 요구된다. 이러한 배경에서 seedless TSV 내 금속 충전 공정에 대한 연구 필요성이 대두되고 있다.

3. Seedless TSV 내 금속 충전 기술의 접근 방식

Seedless TSV 내 전도성 물질(주로 Cu) 충전 기술은 기존 시드층 형성 공정의 복잡성과 비용 문제를 완화할 수 있는 대안으로 꾸준히 연구되고 있다. 일부 연구에서는 seedless TSV 내의 금속 충전을 사용하면 공정 원가가 80 %가 감소하며, 단차가 심한 측벽이나 종횡비 20의 TSV 구조에서도 Ni/Cu 층이 안정적으로 형성된다고 보고되었다.17)

Meng 등18)은 seedless TSV 내 금속 충전 연구에서 전해도금, Cu 페이스트 충전재, 은 나노와이어(Ag nanowire, AgNW) 전기전도성 접착제(electrically conductive adhesive, ECA) 등 다양한 새로운 방식이 시도되었음을 보고하였다. 특히 사물인터넷(Internet of Things, IoT)와 미세전자기계 시스템(micro-electro-mechanical systems, MEMS) 등의 유연 전자 응용에서 이러한 seedless TSV 내 금속 충전 기술의 접근은 점차 연구가 증가되고 있으며, 간단한 공정으로도 높은 금속 충전 효율과 전기적 특성을 확보할 수 있는 가능성을 보여주었다. Su 등8)은 ultra-deep TSV에서 무전해도금을 적용해, 별도의 ALD, PVD 공정 없이 안정적인 충전 특성을 확보할 가능성을 보였다. 이는 저온, 저비용으로 공정을 단순화할 수 있으며, 차세대 이종 집적 및 멀티 칩렛 패키징 요구에 부합하는 실질적 대안이 될 가능성을 제시하였다.

3.1. 첨가제 제어에 의한 TSV 내 Cu 전해도금: seed와 seedless 금속 충전

TSV 내부 Cu 충전을 위한 전해도금에서 첨가제는 시드층의 존재 여부와 관계없이 충전 균일성과 기공 없는 충전을 결정하는 핵심 인자로 작용한다.

첨가제는 억제제, 가속제, 평활제로 구분되며, 각각 Cu 전착 반응을 서로 다른 방식으로 조절하는 화학적 특성을 가진다.19) 첨가제 제어를 통한 bottom-up 충전은 비아 하단부 성장 속도를 상부와 측벽보다 빠르게 유도하는 초고이방성 전착(superconformal deposition) 원리에 따른다. 대표적인 모델로는 가속제 농도 구배를 이용한 곡률 강화 흡착 농도(curvature enhanced adsorbate concentration, CEAC) 모델과 억제제 흡착 및 탈착 거동을 이용한 s형 부성 미분 저항(sshaped negative differential resistance, SNDR) 모델이 있다. 두 모델 모두 첨가제 농도의 정밀 제어가 필요하다.20)

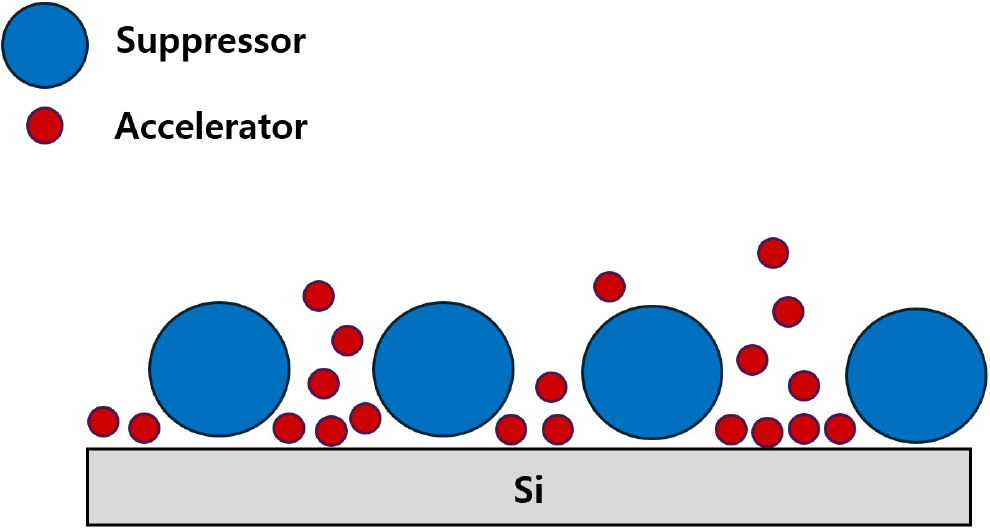

Fig. 2는 S-NDR 모델로 억제제와 가속제가 전극 표면에 경쟁적으로 흡착하는 메커니즘을 단순화하여 나타낸 도식이다. 초기에는 억제제가 전극 표면에 우선적으로 흡착한 후, 시간이 지남에 따라 가속제가 이를 점진적으로 치환함으로써 하부 전착을 유도하는 과정을 보인 것이다.

첨가제의 조성과 상호작용 효과, 농도 제어에 대해 다양한 실험적 접근이 진행되고 있으며, 각 첨가제 간의 관계를 이해하는 것이 충전 성능 향상에 중요한 역할을 한다. 먼저 시드층이 존재하는 TSV 내 Cu 전해도금에서의 첨가제를 사용한 충전 연구들에 대해 살펴본다.

최근 Zhao 등21)의 연구에 따르면, TSV 내부의 Cu 충전 과정에서 억제제(polyethylene glycol, PEG)와 가속제(bis(3-sulfopropyl) disulfide, SPS)를 함께 첨가하여 불완전한 충전 문제를 개선할 수 있음을 확인하였다. 특히 64 mol/m2 PEG와 4 mol/m2 SPS 조건에서 기공 없는 충전이 이루어졌으며, PEG의 농도가 56, 48, 40 mol/m2로 감소할 경우, TSV 측벽에서 Cu의 빠른 성장 속도로 인해 TSV 입구가 조기에 폐쇄되어 내부에 기공이 남는 충전 불량이 발생하였다. 이는 억제제의 표면 코팅률이 농도에 따라 크게 달라지기 때문이다.

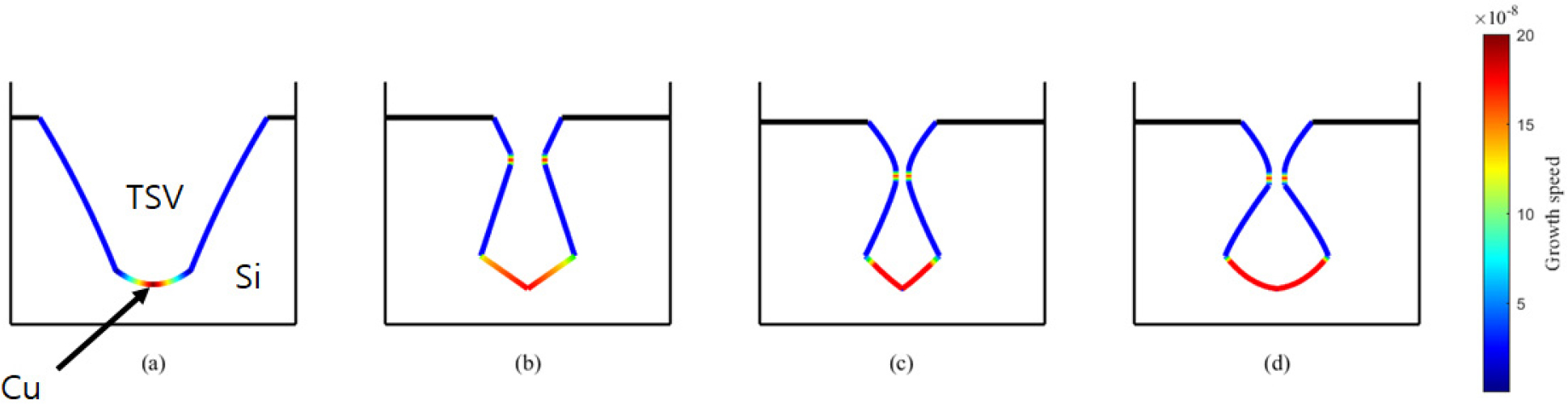

Fig. 3는 Zhao 등21)의 결과를 억제제 농도 변화에 따른 TSV 내 Cu 충전 거동 시뮬레이션 결과를 나타냈다. (a-d)는 억제제(PEG) 농도가 64, 56, 48, 40 mol/m2일 때의 성장 속도 분포를 보여주며, 억제제 농도가 낮아질수록 비아 입구가 조기에 폐쇄되어 내부에 빈 공간이 남는 경향이 뚜렷해진다.

Schmitt 등22)은 억제제만을 사용하는 단일 전해액에서도 Cu의 bottom-up filling이 가능함을 확인하였다. 이들은 Tetronic 701과 chloride 혼합 전해액에서 S-NDR 모델을 적용하였으며, chloride 농도를 1 mM에서 80 µM으로 낮추고 전위 스텝을 -500 mV에서 -560 mV로 조절함으로써 충전 시작 위치를 제어하였다. -500 mV에서는 바닥 성장, -560 mV에서는 상부 성장으로 전환하는 passive-active transition 거동이 관찰되었으며, 충분한 time-step 유지 시 기공 없이 충전이 달성되었다. 따라서 전해질 조성과 전압 제어가 국소 도금 전환과 Cu 충전 균일성에 결정적 영향을 미침을 보였다.

반면 Wang 등23)은 다중 첨가제 시스템의 복잡성을 줄이기 위해 에틸렌-프로필렌 산화물 공중합체(ethylene-propylene oxide copolymer, EPE)와 같은 고분자 단일 첨가제를 적용하였다. 농도와 전류 밀도 조건을 달리하며 충전률을 분석한 결과, 0.002 g/L 저농도 EPE에서 0.3 A/dm2 (ASD)에서 Cu 충전률 100 %, 0.1 ASD에서 약 95 %를 달성하였다. 0.5 및 0.7 ASD에서는 각각 79 %, 70 %로 하단에 기공이 발생하였다. 0.02 g/L 고농도에서는 계면활성제 분자 집합체(micelle) 형성으로 억제 효과가 저하되어 충전률이 감소하였다. 저농도에서는 음극 표면에 평탄하게 흡착해 비아 입구 성장을 억제하고 하단 성장을 유도해 Cu의 bottom-up 충전을 달성할 수 있다.

Zhang 등24)은 polyether 구조에 thioether를 도입한 신규 억제제를 개발하여 전극 표면 흡착력을 강화하였다. 이는 기존 100~300 ppm보다 낮은 농도에서도 결함 없는 충전이 가능하게 했으며, 전기화학 분석에서 고농도에서 높은 분극 강도와 농도 의존성을 보여 Cu의 TSV 상부 전착을 억제하고, 하부에서는 bottom-up 성장을 촉진하였다. 특히 폭 70 nm 트렌치에서 분자량 1,000의 thioether 변성 PEG (PEG1000-S)를 적용하여 결함 없는 bottom-up Cu 충전을 수행하였다. 이를 통해 변성 polyether가 TSV 내 전해도금의 충전 균일성을 크게 향상시킬 수 있음을 확인하였다.

이와 같이 시드층이 존재하는 TSV에서의 전해도금 연구는 첨가제의 농도, 전위 조건, 분자 구조가 충전 균일성을 결정하는 요소로 확인되었다. 이러한 전해도금 메커니즘을 seedless TSV 내 금속 충전에도 적용할 가능성을 모색하는 연구가 진행되고 있다.

Guo 등19)은 할라이드 이온(Cl-/I-), SPS, PEG, 평활제로 구성된 첨가제가 시드층 유무와 관계없이 전착 형태와 결정 구조를 제어하는 핵심 요소임을 정리하였다. 이들은 가속제와 억제제의 경쟁적 흡착-탈착 거동이 bottom-up superfilling을 가능하게 한다고 설명하였다. Cl- 농도가 수 mM 수준에서 PEG의 억제 효과를 안정화시키고, 수 ppm 농도의 SPS가 비아 하단에서 국소적으로 도금 속도를 가속하는 조건에서 기공 없는 충전이 구현될 수 있음을 제시하였다.

Im 등25)은 ALD로 증착한 Ru 배리어 위에서 시드층 없이 Cu를 전해도금하며 PEG와 야누스 그린 B (Janus green B, JGB) 첨가제의 영향을 분석하였다. 첨가제를 사용하지 않은 경우 Cu의 핵 생성 밀도가 낮고 핵 크기가 불균일하여 기공 발생 가능성이 높았으나, PEG와 JGB를 함께 첨가하면 작은 크기의 균일한 핵이 고밀도로 형성되어 균일하고 기공 없는 Cu 층을 구현할 수 있었다. 이는 seedless TSV 내 금속 충전에서도 첨가제 설계가 초기 핵생성과 성장 안정성을 확보하는 데 결정적임을 실험적으로 입증한 것이다.

Wang과 Le26)은 seedless TSV 내 금속 충전에서 단일 첨가제 SH110 (3-(2-(4,5-dihydrothiazol-2-yl)disulfanyl) propane-1-sulfonic acid)을 적용하여 직경 20 µm, 깊이 60 µm TSV에서 Cu 전해도금을 수행하였다. 1 mA/cm2 전류 밀도에서 12 h 도금한 결과, SH110을 사용한 경우 기공 없는 완전 Cu 충전이 달성된 반면, 기존 SPS 첨가에서는 기공이 발생하였다. 전기화학적 분석에는 SH110이 기존 SPS 첨가 대비 안정적인 전착 특성을 보여 bottom-up Cu 충전에 유리함을 확인하였다. 이 결과는 seedless TSV 내 금속 충전에서 단일 첨가제를 이용한 기공 없는 Cu 충전의 가능성을 제공한다.

따라서 기존 시드 공정에서의 첨가제 제어 원리가 seedless TSV 내 금속 충전 연구로 확장되며, 기공 없는 충전을 달성하기 위한 새로운 방향을 제시하고 있다.

3.2. 배리어/시드층을 겸하는 Seedless TSV 내 금속 충전 기술

Table 2는 seedless TSV 구현을 목표로 배리어와 시드 역할을 겸하는 기능성 금속층의 소재, 공정 조건, 적용 TSV 크기, 특징을 정리한 것이다. 기존 TSV 내 충전 공정에서는 시드층의 단차 피복률과 시드층 산화가 충전 결함의 주요 원인으로 지적된다. 이를 극복하기 위해 별도의 PVD/ALD로 시드층을 증착하지 않고 무전해/전해 합금 도금을 통해 배리어와 시드 기능을 동시에 수행하는 층을 형성하는 연구가 진행되고 있다. 이 합금층은 전통적 의미의 시드층이 아닌 배리어/시드 역할을 겸하는 기능성 금속층으로, 후속 Cu 전해도금이 직접 가능하다는 점에서 seedless 접근으로 분류된다. Table 2에 제시된 사례들은 이러한 전략의 구현 예로, 공정 단순화, 시드층 관련 결함 감소, 충전 성능 향상 및 비용 절감 효과를 기대할 수 있다.27)

Table 2.

Summary of barrier/seed substitute layers for seedless TSV filling.

|

Barrier/seed substitute layer | Process Conditions |

TSV size (diameter × depth) | Key features | References |

| Dual-catalyst ELD-Ni | Pd2+-activated PI | Φ 70 µm × 530 µm |

Uniform filling; low leakage; high-aspect-ratio compatible | Su et al. (2024)8) |

| Diazonium ELD-Ni-B |

Ni3B (6.1 wt% B); 60 min | Φ 9 µm × 110 µm |

Void-free; Cu diffusion barrier | Zeb et al. (2024)27) |

| ELD-Ni-P | DBDAa) additive | / |

Strong adhesion; amorphous Ni-P; dual barrier/seed | Buylov et al. (2023)28) |

|

Electroplated Ru-W alloy barrier |

3-5 mA/cm2; pulse-reverse | / |

Continuous interface; stable coating | Santos et al. (2022)29) |

|

Electroplated Co-W alloy barrier |

pH 3.5; 10-20 mA/cm2 | / |

Dense Cu layer; high efficiency | Santos et al. (2021)30) |

Su 등8)은 폴리이미드(polyimide, PI) 절연층 표면을 알칼리 환경에서 개질하여 폴리아미드산(polyamide acid, PAA) 층을 형성하고, 이를 통해 Pd2+ 흡착을 촉진하는 이중 촉매 무전해 Ni 도금 공정을 제안하였다. 형성된 층은 배리어와 시드 기능을 동시에 수행하며, 고종횡비 TSV에서도 균일한 충전이 가능하였다. X선 광전자 분광법(X-ray photoelectron spectroscopy, XPS) 분석에서는 PI 표면의 imide 구조가 amide 구조로 전환되고 -COO-기가 노출되어 Pd2+ 흡착이 증가함을 확인하였다. 직경 70 µm, 깊이 530 µm TSV에서 20 V 동작 시 정전용량 1.3 pF, 누설전류 1.7 pA로 측정되었으며, 이를 통해 Ni 층의 배리어 기능과 시드층의 기능을 수행함을 확인하였다.

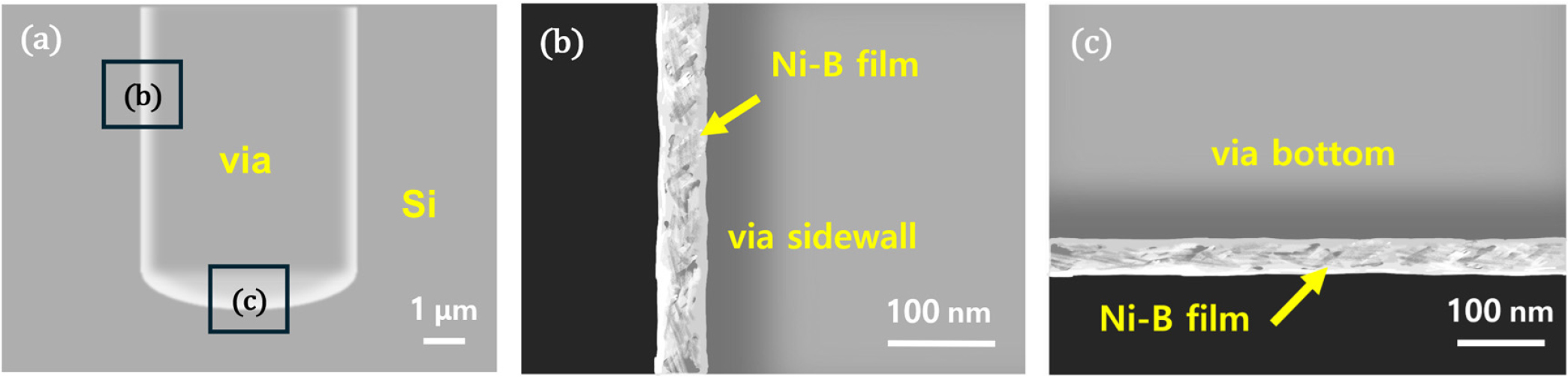

Zeb 등27)의 최신 연구에서는 diazonium 화학법을 이용해 실온에서 SiO2 표면을 전처리 없이 개질한 후 무전해 Ni-B 합금층을 도금하여 배리어/시드층 기능을 동시에 확보하는 단일 단계 공정을 제안하였다. 형성된 Ni-B 층 위에서 직경 9 µm, 깊이 110 µm TSV를 60 min간 Cu 전해도금한 결과, 균일한 충전과 뚜렷한 결정 배향이 관찰되어 전기적 성능에 유리함을 보였다. 이후 XPS와 에너지 분산형 X선 분광법(energy dispersive X-ray spectroscopy, EDX) 분석에서 6.1 wt% B가 포함된 Ni3B 상이 확인되었으며, 이는 Cu 확산 차단에 효과적임을 보여준다. 이러한 diazonium 표면 개질과 자가촉매 무전해도금 공정은 차세대 고종횡비 TSV 배리어/시드층 코팅 기술로 활용될 가능성을 보였다.

Fig. 4는 TSV 내부에 형성된 Ni-B 층을 모식도로 나타내 (a)는 전체 비아 단면, (b)는 측벽, (c)는 바닥 영역을 보인 것이다. 이를 통해 핀홀(pinhole)이나 결함 없이 연속적이고 균일한 층이 형성됨을 확인하였고, Ni-B 층이 실제 구조 내부에서도 안정적 코팅성을 확보함을 시각적으로 보여주며, 배리어 및 시드층으로서의 실효성을 뒷받침할 수 있다.

Buylov 등28)은 무전해 Ni-P 도금을 TSV의 배리어/시드층으로 적용하여 비정질 및 나노 결정 구조가 동시에 나타나는 층을 형성하였고, 이는 높은 안정성과 Cu/SiO2 계면에 대한 우수한 접착 특성을 제공하였다. 또한, 유기 첨가제(4,4dithiobenzene disulfonic acid, DBDA)를 활용해 미세구조를 제어함으로써 배리어층과 시드층을 동시에 기능할 수 있음을 보였다.

Su 등8)의 연구가 수백 µm 급 고종횡비의 TSV 내 Cu 충전에 적합함을 보인 반면, Zeb 등27)의 연구는 수십 µm 규모의 TSV 내 Cu 충전이 가능함을 보였다. 이는 무전해법을 사용한 seedless TSV 내부의 Cu 충전 기술은 시드층 형성 공정을 생략하면서도 균일한 Cu 충전과 후속 접합 공정에서 안정적인 인터커넥션을 구현에 기여할 수 있음을 의미한다. 한편, 무전해 합금층과 함께 전해 합금층을 적용하여 배리어/시드 기능을 동시에 확보하려는 연구도 제시되고 있다.

Santos 등29)의 연구에 따르면, Ru 소재는 낮은 저항과 우수한 Cu 접착력, seedless 전해도금 호환성을 제공하여 대체재로 검토되고 있다. 특히 Ru-W 합금은 배리어층과 전기적 특성을 제공하여 직접 Cu 전해도금이 가능했다. 실험 결과, 균일한 코팅성과 막의 연속성을 확보하려면 최소 3-5 mA/cm2 이상의 전류 밀도가 요구되었다. 낮은 전류 밀도에서는 입자 크기가 수 µm 수준으로 커지고 핵생성 밀도가 낮아졌다. 전류 밀도가 증가하면 작은 입자가 다수 형성되었으며, pulse-reverse 전류를 적용할 경우 입자 크기가 감소하고 표면 거칠기가 개선되었으나, 큰 입자의 형성을 완전히 억제하지는 못하였다. EDS 분석에서는 Ru-W/Cu 계면의 연속성이 확인되었으나, 합금층의 균일성과 장기적 신뢰성은 개선이 필요하며 전기적 저항 및 열적 안정성에 대한 추가 평가가 요구된다.

또한, Santos 등30)은 별개의 연구에서 Co-W 배리어가 기존 Ta/TaN 대비 낮은 저항, 강한 Cu 접착력, 우수한 배리어층의 성능을 갖추며 시드층 없이도 Cu 도금이 가능한 차세대 소재 후보로 언급하였다. Cu/Co-W 계면의 접착력은 기존의 Cu/Ta 계면보다 높아 전자마이그레이션 수명 개선에도 유리하였다. Seedless TSV 내 Cu 도금 특성은 전해액의 pH와 전류 밀도에 크게 의존하였다. pH 3.5의 약산성 용액에서는 연속적이고 치밀한 Cu 층이 얻어졌으며, Cu 층의 두께는 약 0.8-0.9 µm, 도금 효율은 거의 100 %로 보고되었다. 전류 방식에 따라 미세구조가 달라졌는데, 직류(10 mA/cm2, 225 s)에서는 평면적이고 연속적인 Cu 층이 형성되었고, 펄스 전류(> 20 mA/cm2)에서는 핵생성 사이트가 포화되어 성장이 가속화되는 경향이 나타났다.

Jang과 Jung31)은 Bosch 공정에서 형성되는 단차가 누설 전류, 배리어/시드층 불연속, Cu 충전 결함의 주요 원인임을 유한 요소 해석(finite element analysis, FEA) 및 TEM 분석으로 확인하였다. 이를 억제하기 위해 cryogenic 플라즈마(-100 °C 이하), SF6/O2 혼합가스 1-step 플라즈마, 펄스폭 1.5 s 이하 조건 등을 적용하여 scallop-free TSV를 구현하였다. 이 조건에서 배리어/시드층 두께를 기존 대비 약 1/4 수준으로 줄인 상태에서도 고속 Cu 도금으로 결함 없는 충전이 가능함을 제시하였다.

결과적으로 무전해 합금층과 전해 합금층은 배리어/시드층 기능을 동시에 수행할 수 있어 seedless TSV 내 Cu 충전에 활용될 가능성을 제시한다. 다만, 코팅층의 균일성, 전기 저항성, 장기적 신뢰성 확보는 향후 해결해야 할 과제로 남아 있다.

3.3. 금속 나노와이어 및 페이스트를 이용한 seedless TSV 내 금속 충전 기술

Ag 나노와이어 또는 Cu 나노/마이크로 입자를 포함한 페이스트를 충전재로 하여 TSV 안을 직접 채우는 충전 기술은 높은 충전률과 우수한 전기적 특성을 확보할 수 있는 가능성이 제기되고 있다.32) Zhao 등21)은 AgNW가 포함된 ECA를 충전재로 적용하였다. 이들은 직경 100 µm, 깊이 625 µm TSV 내부를 실온에서 충전하였으며 30~40 wt% AgNW 조건에서 저항률은 4.8 × 10-3~6.0 × 10-4 Ω・cm, 개별 TSV 저항은 7.5 Ω이었다. 이는 나노와이어 네트워크가 전도 경로를 형성하여 저온 공정에서도 안정적인 seedless TSV 내 금속 충전이 가능함을 제시하였다.

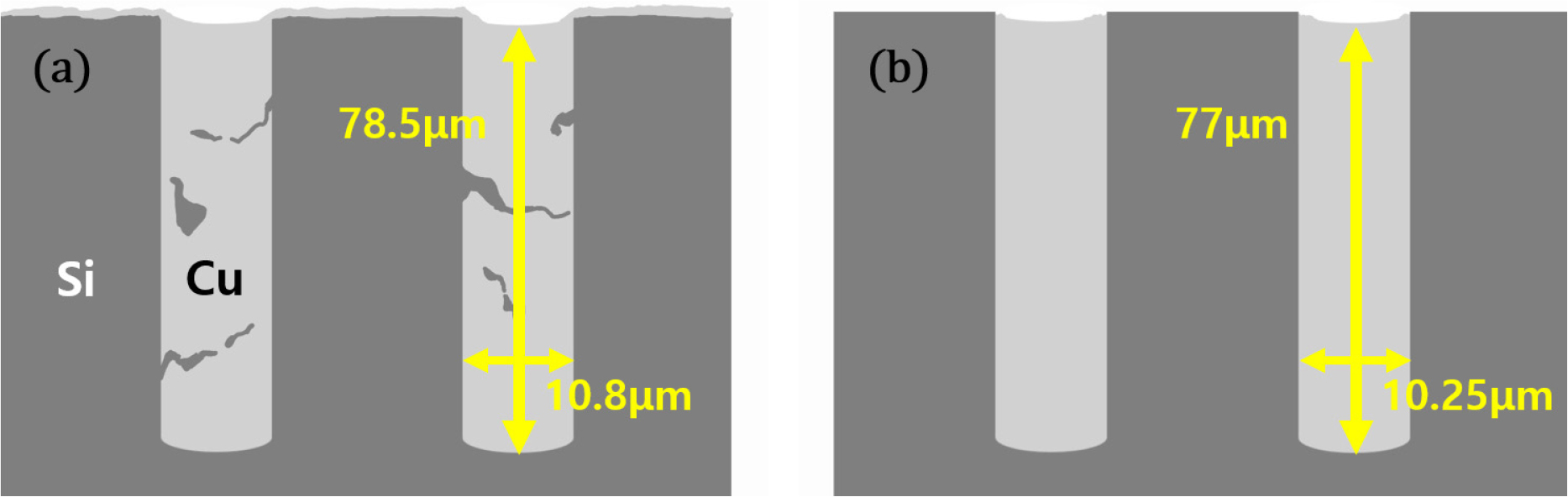

최근 Hoang 등33)은 시드층 증착 한계를 극복하기 위해 구리 입자가 포함된 Cu 페이스트를 충전재로 사용한 seedless TSV 내 Cu 충전 공정을 제안하였다. Sub-µm급 Cu 입자로 구성된 저점도 페이스트는 과잉 코팅(overburden)과 대형 기공 없이 균일한 충전을 달성했으며, 이와 같은 충전 거동은 Fig. 5를 통해 명확히 확인할 수 있다. 고점도 Cu 페이스트 A를 사용할 경우, 과잉 코팅과 균열, 내부 기공이 발생하였고, 저점도 Cu 페이스트 B를 사용할 경우 균일하고 결함 없는 충전이 이루어졌다. 진공 프린팅 후 250 °C에서 10~20 min 소결 시 저항률은 4~5 µΩ・cm, 260~270 °C 소결 시 3 µΩ・cm까지 감소하였다. 이는 입자 간 neck 성장과 기공 감소에 기인하며 미세 기공은 열적, 기계적 응력 완화에 기여한다. 이러한 결과는 화학적 기계적 연마(chemical mechanical planarization, CMP) 공정을 생략하면서도 낮은 저항과 높은 충전 성능을 동시에 달성할 수 있는 공정 단순화의 장점을 보여준다.

한편, Ejiri 등34)은 Cu-SnBi 복합 페이스트를 충전재로 이용해 TSV 내부를 충전한 뒤, 열사이클 및 초가속스트레스 시험(highly accelerated stress test, HAST) 등의 신뢰성 시험을 수행하였고, 전기적 특성이 안정적으로 유지됨을 확인하였다. 이는 페이스트를 충전재로 이용한 seedless TSV 내 금속 충전 공정이 전기적 성능뿐 아니라 장기적 신뢰성 측면에도 적용 가능함을 제시하였다.

3.4. Seedless TSV 내 금속 충전 기술의 한계

Seedless TSV 내 금속 충전 기술은 공정 단순화와 비용 절감의 장점을 제공하지만, 전기적 특성과 신뢰성 측면에서 여전히 한계를 갖는다. 금속 페이스트를 이용한 금속 충전은 수 µm 이하의 작은 직경의 TSV에서 충전 밀도 확보가 어렵고, Cu 입자의 산화와 내부 기공 형성으로 인해 저항 상승 및 전자마이그레이션 취약성이 발생한다.4) 또한 고종횡비 seedless TSV에서 전해도금을 적용할 때, 내부 하단부에서 Cu 이온 농도 저하와 확산 한계가 나타나 충전이 불완전해지며, 억제제 농도와 전류 밀도에 따라 seam이나 기공이 발생할 수 있다.10) 이러한 점은 seedless TSV 내 금속 충전만으로는 차세대 집적 요구를 충족하기에는 아직 제한이 있음을 보인다. 따라서 seedless TSV 내 금속 충전 기술은 후속 접합 공정과의 공정 연계 연구의 필요성을 제기하고 있으며, 최근 일부 연구에서는 TSV 내 금속 충전-평탄화-하이브리드 본딩을 하나의 통합 프로세스로 구현하려는 시도를 보이고 있다.

4. TSV 내 도금 공정 기술과 하이브리드 본딩법의 연계 가능성

Table 3은 TSV 공정의 Cu filling-CMP-hybrid bonding 연계를 한눈에 보여주며, TSV filling method, Cu filling 시 특징, 표면 처리, 본딩 타입(D2W, W2W 등)을 체계적으로 정리한 것이다. 최근 Lee 등35)의 연구 결과에 따르면, 16단 이상 HBM 적층에는 범프리스 하이브리드 본딩 기술이 요구된다. 하이브리드 본딩은 TSV와 Cu 패드를 CMP를 통해 평탄화하고, 플라즈마 및 탈이온수(deionized water, DI) 세정 공정을 통해 표면에 -OH기를 활성화한 후 저온에서 산화막-산화막 결합을 형성한다. 이후 어닐링 과정에서 Cu 확산에 의해 최종 Cu-Cu접합이 형성된다. 이들은 CMP 조건 조절과 백 엔드 오브 라인(back-end-of-line, BEOL) 구조 제어를 통해 Cu 패드의 디싱과 프로파일(profile) 변형을 감소시켰다. 이를 통해 16단 HBM 적층에서 기공 없는 본딩과 안정적인 전기적 수율을 확보함을 실험적으로 확인하였다.

Table 3.

Summary of Cu filling-CMP(Chemical Mechanical Polishing)-hybrid bonding processes in TSV integration.

| TSV Filling Method |

Cu Filling Characteristics | CMP / Surface Treatment | Bonding Type | Reliability / Remarks | References |

| / | / | CMP planarization; plasma + DI rinse for -OH activation | D2W (Die-to-Wafer) hybrid Cu-Cu | 16H HBM (High Bandwidth Memory) stack; optimized CMP ensured stable yield | Lee et al. (2024)35) |

| Cu Electroplating on PVD Cu seed layer |

Void-free Cu filling (AR = 10); Cu dishing 2.5 nm, SiO2 0.5 nm after CMP | CMP optimized to minimize Cu/SiO2 erosion | W2W (Wafer-to-Wafer) hybrid Cu-Cu | Defect-free interfaces; reliable 3-wafer stacking | Arnaud et al. (2020)4) |

| Bottom-up Cu Electroplating (Ti-Cu barrier/seed) |

Uniform TSV reveal (AR = 6, thickness 22 µm) | CMP + ELD Ni-B plating (65 °C, 50-100 nm) + TMAHa) etch | TSV-Cu hybrid bonding | SiO2-SiO2 and TSV-Cu bonded | Watanabe et al. (2020)37) |

| Cu Electroplating with barrier/seed deposition | Optimized CMP for barrier height control | CMP + plasma activation for bonding | C2W (Chip-to-Wafer) hybrid bonding | Clean surface > 99.5 % yield | Besi and Applied Materials (2023)38) |

| Cu Electroplating | Cu protrusion 16.8 nm | CMP control for self-compensation | W2W hybrid bonding | Peel stress 165 MPa; balanced protrusion/dishing | Wang et al. (2022)39) |

| Cu Electroplating on Ti/Cu seed | Roughness < 3 nm; height variation < 20 nm | Optimized CMP for smooth Cu/polymer interface | Cu/polymer hybrid bonding | R 10-8 Ω; ∆R < 3 % (TCT 750 cycles), < 5% (HAST 264 h) | Lin et al. (2025)40) |

또한, Joo 등36)은 die-to-die 간격이 10 µm 이하로 줄어드는 HBM4 이후 세대에서는 기존 언더필과 열압착 방식이 한계에 부딪히며, 하이브리드 본딩으로의 전환이 필요함을 강조하였다.

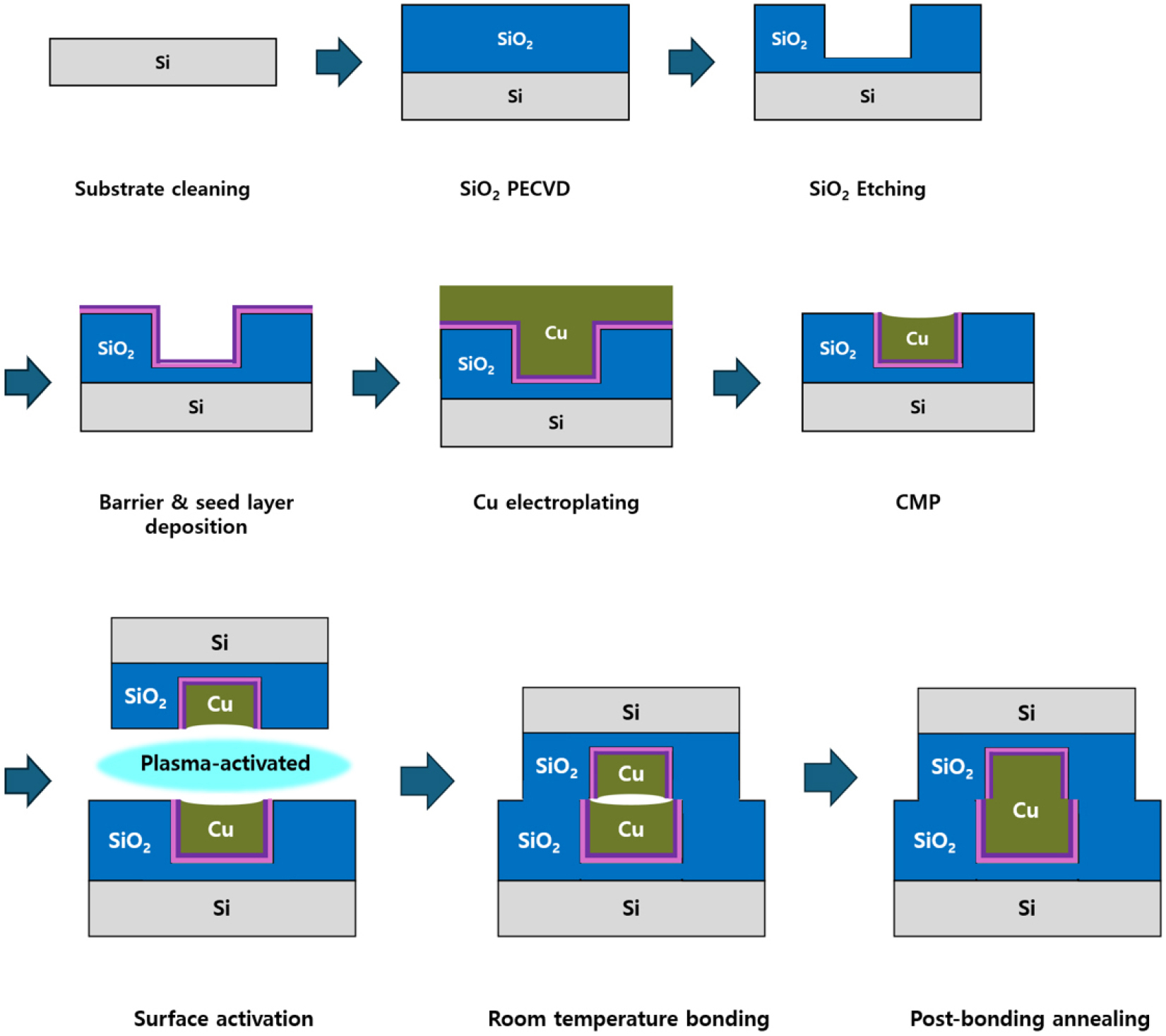

Fig. 6은 TSV 내부의 도금 및 하이브리드 본딩 공정을 단계별로 도식화한 그림이다. 실리콘 기판 상에 SiO2 절연층 형성부터 비아 식각, 배리어 및 시드층 증착, Cu 전해도금 및 CMP, 이후 플라즈마 표면 활성화와 실온 본딩 및 어닐링으로 이어지는 전체 공정 흐름을 보인 것이다.

최근 연구에서는 TSV 내 전해도금과 Cu-Cu 하이브리드 본딩을 연계해 다른 기종 웨이퍼의 3차원 집적 구조 구현을 위한 공정 개발이 활발히 진행되고 있다. TSV 내부 충전율이 올라가 결함(seam, 기공)이 줄어들수록, 하이브리드 본딩 시 실효 접촉면적이 커지고 접촉저항이 낮아지는 방향으로 작용한다. TSV 충전은 기판 간을 연결하는 Cu 배선을 형성하는 metallization 단계이므로, 이러한 기공은 전도 경로의 연속성을 저해해 접속 저항을 증가시킨다. 전해도금 조건이 TSV 충전 품질을 좌우하며, 적절히 제어되면 무결함 충전이 가능하지만 제어가 부족하면 seam, 기공과 같은 결함이 형성된다. Zhao 등41)은 금속 배선에서의 기공 형성은 저항 상승의 직접 원인으로 보고하였다.

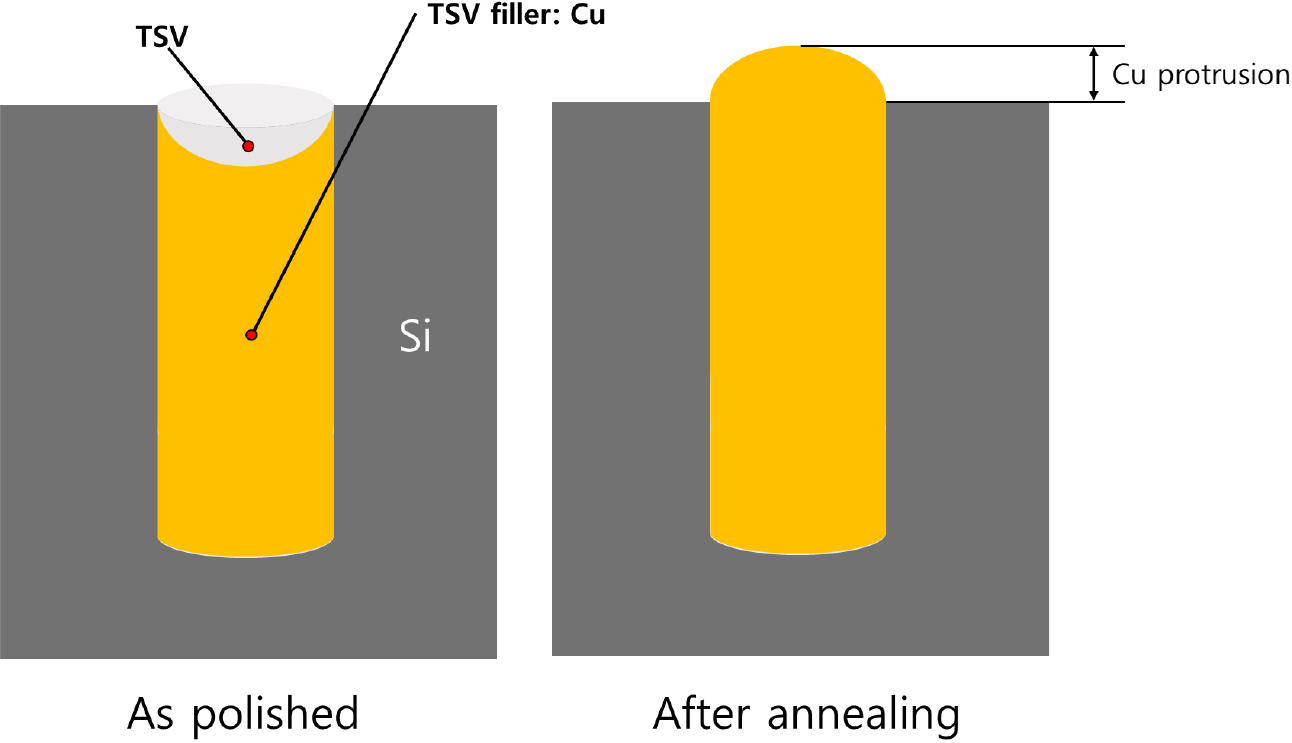

Fig. 7은 TSV에서 Cu protrusion을 간단하게 묘사한 그림이다. Protrusion은 열 처리 동안 CTE 불일치와 응력 완화로 충전된 Cu가 주변 SiO2보다 살짝 위로 솟는 현상이며, 수 nm 차이도 본딩 접속에 영향을 준다. 한편 TSV 도금 단계에서 Cu filling ratio 증가는 seam, 기공 억제와 미세조직의 방향성 제어를 통해 protrusion의 민감도를 완화하는 효과가 더 두드러진다.42) 반면 하이브리드 본딩 단계에서는 수 나노미터 수준의 Cu protrusion이 접촉면 형성과 접촉저항을 좌우하므로, 적정 범위의 protrusion이 확보될수록 접촉저항이 유의하게 낮아지는 경향이 보고되어 왔다. Watanabe 등43)에 따르면, 상부 TSV 기판의 Cu protrusion이 4.0 nm, 하부 Cu 전극 기판의 Cu protrusion이 4.8 nm일 때 기판의 접촉저항은 약 3.5 Ω이 나왔고, 상부 TSV 기판의 Cu protrusion이 7.7 nm, 하부 TSV 기판의 Cu protrusion이 29 nm일 때 기판의 접촉저항은 100 mΩ 미만으로 측정되었다. 따라서, Cu protrusion이 큰 기판을 사용하여 연결할 경우 접촉부에 stress가 집중되어 산화막이 쉽게 깨지고 전도 경로가 보다 쉽게 형성되어 접촉저항이 크게 감소함을 확인할 수 있다. 따라서 충전율을 높여 결함을 줄이고 미세조직을 정돈한 뒤 CMP로 높이 프로파일을 설계해 본딩 단계에서 목표 protrusion을 확보하는 접근이 합리적이다. 표면적으로는 도금 단계에서의 protrusion 저감과 본딩 단계에서의 protrusion 확보가 상충되는 듯 보이지만, 전자는 내부 결함과 미세조직에 기인한 열응력 거동의 제어, 후자는 본딩 시 계면에서의 접촉 경로 형성이라는 서로 다른 기전에 기반하므로 상보적 최적화가 가능하며, 두 단계의 정량 상관과 공정 도출에 관한 추가 연구가 이뤄진다면 하이브리드 본딩 기술의 고도화를 견인할 것으로 기대된다.

Arnaud 등4)은 300 mm 실리콘 웨이퍼에 멀티 피치(1~4 µm) 단일 레벨 Cu 다마신(damascene) 패턴을 형성하고, 직경 1 µm, 깊이 10 µm의 TSV에서 전해도금 시드층과 주기적 펄스 전류를 적용한 bottom-up Cu 충전 공정을 수행하였다. 그 결과 TSV 상단의 핀칭(pinching) 현상과 기공이 없는 충전이 이루어졌으며, CMP 공정 후 Cu와 SiO2 표면의 디싱과 침식이 각각 2.5 nm, 0.5 nm로 억제되어 하이브리드 본딩 전 고평탄성 조건을 만족시켰다. 이를 통해 wafer-to-wafer 본딩을 구현했으며, 픽셀, 연산, 메모리 등의 기능이 집적된 개별 웨이퍼를 TSV 및 Cu-Cu 접합으로 수직 적층해 웨이퍼의 외곽까지 결함 없는 접합 신뢰성을 확보하였다.

Watanabe 등37)은 후면 가공과 표면 세정 공정을 정밀 제어해 TSV와 하이브리드 본딩 계면의 전기적, 기계적 특성을 개선하였다. 이들은 접합 전 직경 5.5 µm, 깊이 33 µm TSV가 포함된 웨이퍼와 직경 6 µm Cu 전극 웨이퍼를 상온에서 본딩하였다. 이후 65 °C에서 무전해 Ni-B 도금(50-100 nm)과 약 70 °C의 수산화 테트라 메틸 암모늄(tetramethylammonium hydroxide, TMAH) 알칼리성 식각으로 Si 표면과 잔존 Cu를 제거하고 약 5 nm 두께의 비정질 Si 박막을 코팅하였다. 이후 진공도 10-5 Pa 이하, 하중 100 kN 조건에서 접합을 수행한 결과, SiO2-SiO2 및 TSV-Cu 전극 계면 모두 안정적인 접합이 가능하였다. 이 연구는 웨이퍼 두 장의 접합 실험이었으나, 동일 조건에서 지지 유리 탈착과 하이브리드 본딩을 반복할 경우 3장 이상 적층도 가능함을 제시하였다.

Jung과 Jung44)은 Cu-SiO2 하이브리드 본딩에서 CMP 연마 깊이, 플라즈마 처리, KOH 표면 개질 조건에 따른 접합 신뢰성을 분석하였다. Ar/N2 플라즈마를 적용한 경우 SiO2 표면의 -OH 밀도가 13.6 %에서 28.3 %로 증가하였고, 접촉각은 53.5°에서 35°로 감소하였다. 200 °C 저온 조건에서 계면 에너지는 10.69 J/m2로, 기준값(≥ 5 J/m2)의 두 배를 충족하였다. 또한 KOH 처리 시 Si-O-Si 결합이 Si-OH로 전환되어 Cu 표면의 친수성이 증가하였고, 이를 통해 260 °C 미만에서도 안정적인 Cu-Cu 및 SiO2-SiO2 접합이 가능함을 확인하였다.

최근 발표에 따르면 die-to-wafer 하이브리드 본딩에서도 TSV 도금 및 CMP 공정과의 연계가 중요한 요소로 강조되고 있다. 입자 오염은 기공 형성으로 이어져 계면 신뢰성을 저하시킬 수 있고, 유전체 표면의 거칠기와 활성화 성능 또한 접합 강도 확보에 중요하다. 이에 따라 TSV 내 금속 충전-CMP-본딩 각 공정 사이의 대기 시간을 조절하여 수율과 본딩 신뢰성을 유지해야 하며, TSV 내 금속 충전 성능, 표면 청정도, overlay 정밀도 등을 관리하는 통합적 관리(co-optimization) 전략이 필요하다.38)

결론적으로, TSV 내부의 도금과 하이브리드 본딩법 간 공정 연계는 계면의 전기적, 기계적 특성을 동시에 확보할 수 있는 고신뢰성 3차원 집적 시스템 구현의 실질적 토대를 마련할 가능성을 갖는다.

5. 결 론

본 고에서는 AI 반도체와 HBM의 수요 확대에 따라 주목받고 있는 2.5D/3D 집적 패키징 기술을 배경으로, TSV 내 금속 충전과 하이브리드 본딩법의 연구 동향을 검토하였다.

Seedless TSV 내 금속 충전은 첨가제 제어 전해도금, 합금층 형성, 금속 나노와이어 및 Cu 페이스트 충전재 적용 등 다양한 시도가 이루어졌으며, 시드층 생략을 통한 공정 단순화와 비용 절감 가능성을 보였다. 그러나 고종횡비 TSV 내부에서의 금속 충전 균일성, 금속 산화 억제, 장기 신뢰성은 여전히 해결해야 할 과제이다.

또한 TSV 내 금속 충전 공정은 후속 하이브리드 본딩 신뢰성과 연계되어 있다. 최근에는 TSV 내 금속 충전-CMP-계면 활성화를 통합적으로 연구하여 저온에서의 Cu-Cu/SiO2-SiO2 접합과 기공 없는 다층 적층 가능성을 제시하였다.

결론적으로 seedless TSV 내 Cu 충전과 범프리스 하이브리드 본딩법은 AI 반도체와 차세대 HBM 적층에서 성능과 신뢰성, 생산성을 동시에 향상시킬 수 있는 중요 공정으로 부각되고 있다. 향후에는 장기적 신뢰성 확보와 저온 본딩 호환성 검증을 중심으로, 상용화 가능한 seedless TSV 내 금속 충전 및 하이브리드 본딩 프로세스가 구체화될 가능성이 있다.