1. 서 론

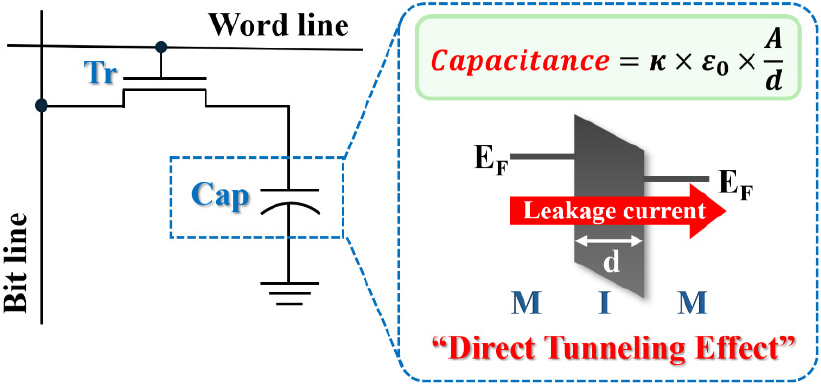

동적 랜덤 액세스 메모리(dynamic random access memory, DRAM)는 PC 및 모바일 기기를 포함한 다양한 응용 분야에서 핵심적인 메모리 소자로 활용되고 있으며, 최근 인공지능 연산을 위한 고성능 컴퓨팅 및 대용량 데이터 처리 수요 증가에 따라, DRAM의 메모리 집적도 향상과 누설전류 감소를 통한 저전력 동작이 필수적인 기술 과제로 대두되고 있다. DRAM 메모리 셀은 하나의 트랜지스터와 하나의 커패시터로 구성된 1T-1C 구조를 가지는데, 소자 미세화가 진행됨에 따라 커패시터 면적이 감소하면서 정전용량(capacitance) 유지와 동시에 누설전류 감소가 가장 중요한 기술적 난제로 작용한다.1,2,3)Fig. 1은 DRAM 커패시터와 직접 터널링(direct tunneling)으로 인해 발생하는 누설전류를 나타낸 개략도이다.

고집적 DRAM 구조의 제한된 셀 면적 내에서 저장된 데이터의 신뢰성은 커패시터의 정전용량에 직접적으로 의존하므로, 충분한 정전용량 확보가 필수적이다. 이를 위해 유전막 두께의 감소와 함께 높은 유전상수(high-𝜅)를 갖는 재료의 적용이 요구되지만, 유전막이 얇아질수록 양자역학적 터널링에 의한 누설전류가 급격히 증가하는 문제가 발생한다. 따라서 등가 산화막 두께(equivalent oxide thickness, EOT)를 효과적으로 감소시키면서도 누설전류를 최소화하는 것이 차세대 DRAM 커패시터 제조의 핵심 기술로 인식되고 있다.1,4,5) 2024 IRDS 로드맵에 따르면, 유전율 50-100을 가지면서 누설전류가 낮은 고유전체의 개발이 요구되고 있다.6)

양산 공정에서는 ZrO2/Al2O3/ZrO2 (𝜅≈38.7) 유전체층과 TiN 전극을 기반으로 한 DRAM 커패시터 구조가 사용되고 있으나, 15 nm DRAM 노드로 스케일링 시 단순한 유전층 두께 감소나 EOT 값 축소만으로는 누설전류 밀도가 증가하는 문제를 피하기 어려웠다. 이를 위해 ZrO2보다 더 높은 유전 상수를 가진 다양한 유전체 소재의 활용이 고려되고 있다.2,7) 이와 함께 열적 안정성, 공정 호환성 및 높은 전도대 오프셋 확보 역시 중요한 요구 조건이다.4,5)

고유전율 재료로는 Si3N4 (𝜅 = 7.5), SixOyNz (𝜅 = 3.9-7.5), Al2O3 (𝜅 = 10), Ta2O5 (𝜅 = 25), ZrO2 (𝜅 = 25), HfO2 (𝜅 = 26), TiO2 (𝜅 = 50) 등 여러 가지 물질이 있으며, SiO2의 상대 유전율인 3.9에 비해 높은 고유전체가 쓰여 왔다.4) 고유전율 유전막 재료 중 TiO2는 높은 유전상수, 화학적 안정성, 무독성 및 풍부한 매장량으로 인해 DRAM 커패시터용 유전체로 주목받고 있다.8) TiO2는 비정질, anatase, rutile, brookite 등의 다양한 결정상을 가지며, 이 중 rutile 상은 약 90-170 수준의 높은 유전상수를 갖는 것으로 알려져 있다. Rutile 상은 일반적으로 600 °C 이상의 고온에서 안정화되는 반면, 비교적 낮은 온도에서 형성되는 anatase 상은 유전상수가 약 30-40 수준으로 낮으며 고온에서 rutile 상으로 상전이되는 구조적 불안정성을 지닌다.8,9,10,11,12,13) 또한, anatase 상 TiO2는 약 3.2 eV의 indirect bandgap을 가지며, rutile 상 TiO2는 약 3.0 eV의 direct bandgap을 가진다.11) TiO2는 이러한 낮은 에너지 밴드갭을 가지고, Si와의 전도대 오프셋(conduction band offset, CBO)이 약 0.1 eV로 매우 작아 누설전류가 크게 증가하는 문제가 존재한다.12) 따라서 DRAM 커패시터에 TiO2를 적용하기 위해서는 유전상수가 큰 rutile 상을 저온에서 안정적으로 형성하는 동시에, 누설전류를 효과적으로 억제할 수 있는 공정 기술의 개발이 필수적이다. 그러나 기존의 rutile TiO2 박막 형성 공정은 일반적으로 400 °C 이상, 경우에 따라 600-800 °C에 이르는 높은 공정 온도를 요구하여 공정 측면에서 한계를 가진다.8,11,13) 일부 수용액 기반 공정이나 anatase-rutile 혼합상을 갖는 원자층 증착(atomic layer deposition, ALD) 공정이 비교적 낮은 온도(200 °C 및 300 °C)에서 보고된 바 있으나, 저온 조건에서 순수한 rutile 상 TiO2 박막을 형성하는 방법은 여전히 제한적이다. 저온에서 rutile TiO2 형성의 어려움이라는 한계를 극복하기 위해 저온에서 물질 증착이 가능한 고반응성의 ALD 공정이 주목받고 있다.8,9) 특히, 플라즈마를 이용하여 반응성을 향상시킨 플라즈마 강화 원자층 증착(plasma-enhanced atomic layer deposition, PEALD)은 보다 낮은 공정 온도에서도 높은 성장률과 우수한 막 품질을 구현할 수 있는 장점을 가진다.9,14)

고유전율 물질인 rutile TiO2를 안정적으로 형성하기 위해서는 열적 ALD로는 쉽지 않다. ALD를 이용하여 rutile TiO2를 형성하려면 격자 불일치가 매우 작은 기판이 필요한데, 특히 RuO2는 rutile TiO2와의 격자 불일치가 작아, 우수한 구조적 정합성을 확보함으로써 누설전류를 감소시키는 효과 또한 가져온다. 이에 따라, rutile TiO2의 안정적인 형성 및 특성 향상을 위해서는 RuO2 intermediate layer가 자주 사용된다.15,16) 하지만 이러한 방식은 공정 단순화 및 양산 적용 측면에서 한계를 보였다.12,15) 한편, rutile TiO2를 저온에서 안정적으로 형성하기 위해 하부 전극의 조성 및 표면 상태가 결정상 형성에 중요한 역할을 한다는 보고가 제시되어 왔다. 이러한 요구 조건을 충족하기 위해, DRAM 커패시터용 전극 재료는 우수한 산화 안정성을 가지며 유전막과의 화학적 반응이 억제되어야 하고, 동시에 높은 일함수를 통해 누설전류를 효과적으로 억제할 수 있어야 한다. 현재까지 DRAM 커패시터 전극 재료로 TiN, TaN 등의 전도성 질화물 및 Ir, Pt, Ru와 같은 귀금속 소재, 격자 불일치도가 낮으면서 열적으로 안정한 MoO3, TaSnOx 등의 전도성 산화물이 연구되어 왔으며, 이 중 TiN은 우수한 열적 안정성, 낮은 전기저항, 그리고 기존 반도체 공정과의 높은 호환성을 동시에 만족시켜, 양산 공정에서 가장 널리 사용되고 있다. 또한, TiN은 약 4.7 eV 수준의 비교적 높은 일함수를 가져 전위 장벽 형성에 유리하며, 금속-절연체-금속(metal-insulator-metal, MIM) 구조의 DRAM 커패시터 전극으로 적합한 재료로 평가받고 있다.17,18,19) TiN은 DRAM의 MIM 커패시터 구조에서 널리 사용되는 금속 질화물 전극으로, 이러한 관점에서 TiN 표면 특성을 제어하여 TiO2 결정상 형성을 유도하는 접근은 의미 있는 연구 방향이 될 수 있다.

이에 본 연구에서는 PEALD와 스퍼터링의 두 방식으로 증착된 TiN 하부 전극과 Ar 플라즈마 전처리 여부에 따른 TiO2 기반의 DRAM 커패시터의 누설전류 및 유전상수를 비교 분석하였다. 각 TiN 하부 전극 위에 동일한 ALD 조건으로 TiO2 유전막을 증착하고, 상부 전극을 형성하여 MIM 구조의 DRAM 커패시터 소자를 제작하였다. 본 연구는 TiN과 TiO2를 모두 PEALD로 증착하고, TiN 하부 전극의 계면을 조절하여 누설전류 개선 및 고유전 특성을 갖는 rutile TiO2를 형성하는 것이 목적이다. 또한, 하부 전극의 물리적, 화학적 특성이 TiO2 유전막의 결정상, 유전특성 및 누설전류 거동에 미치는 영향을 확인하고자 하였다.

2. 실험 방법

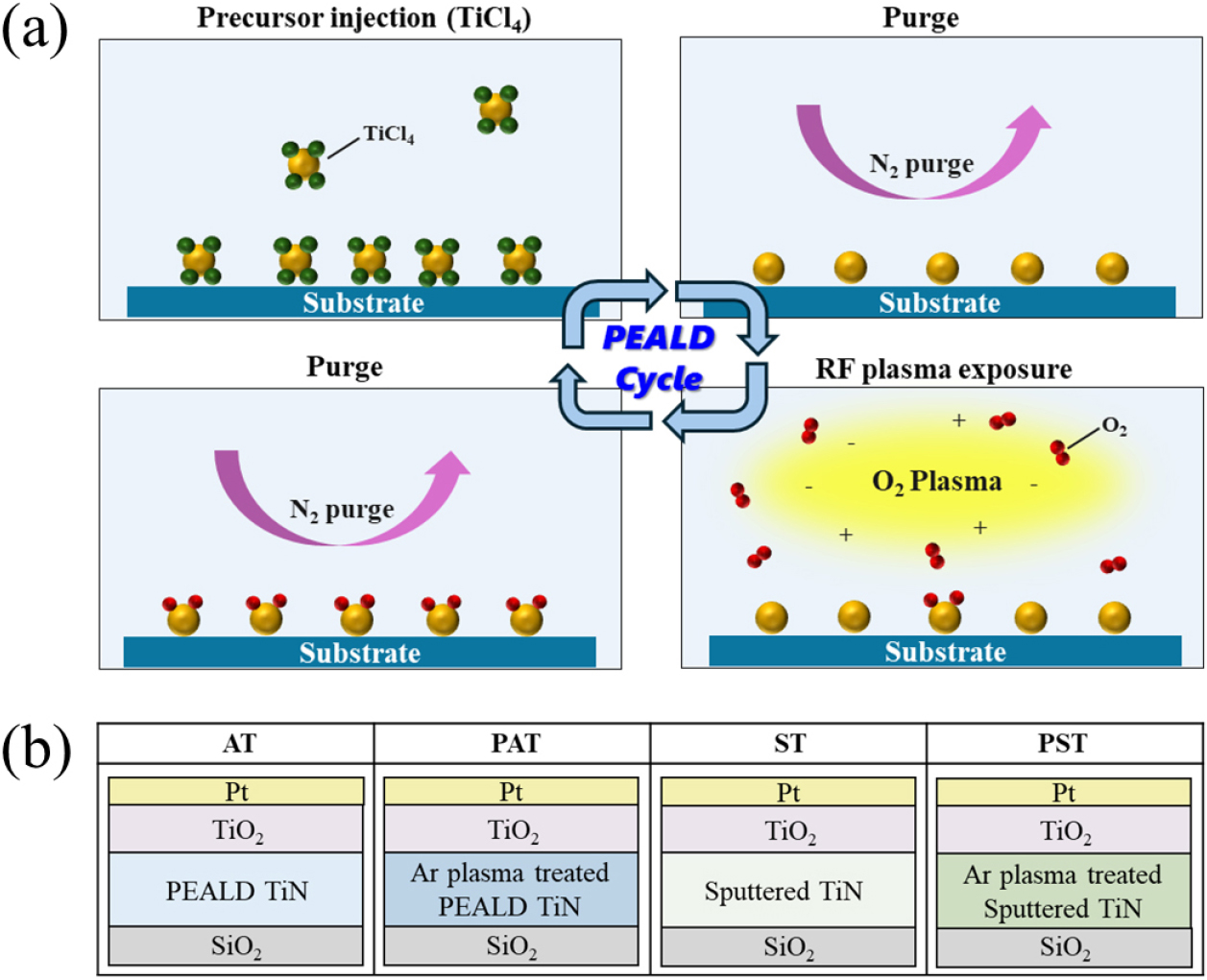

하부 전극의 증착 방법과 하부 전극의 플라즈마 처리 유무에 따른 DRAM 커패시터의 특성 차이를 조사하기 위해 8가지 MIM 구조의 커패시터 샘플을 제작하였다. 하부 전극은 PEALD와 스퍼터 공정을 이용하여 TiN을 증착하였고, 유전막으로는 PEALD를 통해 TiN 하부 전극 위에 세 가지 두께 조건(20 nm, 30 nm, 65 nm)으로 TiO2를 증착하였다. DC 스퍼터링으로 제작한 하부 전극 TiN은 약 80 nm 두께로 증착되었다. 그리고 하부 전극 TiN은 PEALD를 이용해 약 20 nm로 증착되었으며, 388 °C에서 전구체와 반응 가스로 각각 TiCl4, NH3 plasma를 사용하여 TiCl4 dose (1 s) - N2 purge (60 s) - NH3 plasma (15 s) - N2 purge (60 s)의 4가지 단계를 1 cycle로 하여 증착되었다. 특히 플라즈마 소스로 사용된 중공 음극 플라즈마(hollow cathode plasma, HCP)는 고밀도, 고반응성 라디컬 형성으로 인해 낮은 온도에서 기판의 종류와 관계없이 증착된 박막의 결정성을 향상시킬 수 있었다.16,20) TiO2 박막의 경우 300 °C 이상의 온도에서 박막의 결정화가 진행되기 때문에 증착은 313 °C에서 진행되었다.9) 이때, TiCl4와 O2 플라즈마는 각각 TiO2 증착의 전구체와 반응 가스로 사용되었다. Fig. 2(a)는 PEALD의 공정 모식도이다. 전체 PEALD TiO2 증착 공정은 TiCl4 dose (1 s) - N2 purge (60 s) - O2 plasma (15 s) - N2 purge (60 s)의 4가지 단계를 1 cycle로 하여 두께별로 각각 350, 520, 860 cycle 증착되었다. 이때, ALD 공정 전반에 걸쳐 공정압력은 약 0.88 Torr로 유지되었다. TiN과 TiO2의 PEALD 공정 조건은 본 연구 그룹의 선행연구를 참고하여 적용하였다.16,20)

한편, TiO2 증착에 앞서 TiN 하부 전극에 대해 플라즈마 처리기(PDC-32G, Harrick Plasma)를 이용하여 18 W 조건에서 300 s 동안 Ar 플라즈마 처리를 수행하였다. 이후 TiO2를 증착하고, 상부전극으로는 스퍼터링을 이용해 Pt 금속 박막을 유전막 위에 증착하였는데, 이때 쉐도우 마스크를 통해 원형 디스크 전극을 형성하여 단위 소자를 제작하였다. 최종적으로 Pt/TiO2/TiN의 MIM 구조를 갖는 커패시터가 제작되었다.

이러한 구조에서 TiO2 박막은 4가지 다른 표면에서 성장되었다. 4가지 기판의 종류는 Fig. 2(b)에 정리하였는데, PEALD로 증착한 TiN 기판(AT), PEALD로 증착한 TiN에 아르곤 플라즈마 처리한 기판(PAT), sputter로 증착한 TiN 기판(ST), sputter로 증착한 TiN에 아르곤 플라즈마 처리한 기판(PST), 이렇게 4가지 하부 전극 위에 다양한 두께로 TiO2 유전막을 증착하여 8가지 샘플을 제작하였다. AT와 ST 샘플은 유전막 두께에 따라 각각 20 nm, 30 nm, 65 nm 조건으로 제작되었으며, 이에 따라 AT20, AT30, AT65, ST20, ST30, ST65로 각각 명명하였다. 샘플명에 포함된 숫자는 유전막의 두께(nm)를 나타낸다. 반면, PAT와 PST 샘플은 유전막 두께 30 nm 조건에서만 제작되어 각각 PAT30과 PST30으로 표기하였다.

TiN 및 TiO2의 두께는 엘립소미터(FS-1 multi-wavelength ellipsometer, Film-Sense)를 이용하여 측정되었고, 두께와 표면 모폴로지(morphology)는 고분해능 주사전자현미경(high-resolution scanning electron microscope, HR-SEM, Hitachi High Technologies Corporation, SU8010)을 이용해 측정되었다. TiO2 내 Ti 양이온의 면밀도와 박막의 결정성은 각각 X-선 형광 분석(X-ray fluorescence spectroscopy, XRF, US/ARL QUANTX, Thermoscientific)과 경사 입사 X-선 회절(grazing incidence X-ray diffraction, GIXRD, Dmax 2500/PC, Rigaku)을 통해 측정되었다. 원자힘 현미경(atomic force microscopy, AFM, NX10, Park System)을 통해 TiO2 증착 전후의 표면 거칠기를 분석하였고, 박막의 조성은 X-선 광전자 분광기(X-ray photoelectron spectroscopy, XPS, Thermo Fisher Scientific Brno s.r.o, Nexsa)를 이용해 확인되었다. 접촉각 분석 장비(water contact angle analyzer, Phoenix-MT, SEO)를 이용하여 플라즈마 처리 전후 시편의 표면 젖음성(wetting) 변화를 분석하였다. 커패시터 소자의 전류-전압(current-voltage, I-V) 및 정전용량-전압(capacitance-voltage, C-V) 특성을 포함한 전기적 특성은 파라미터 분석기(parameter analyzer, HP-4155, Keithley 4200)를 통해 측정되었다. 유전상수와 EOT는 정전용량으로부터 계산되었으며, 모든 전기적 측정은 상온(25 °C)에서 진행되었다.

3. 결과 및 고찰

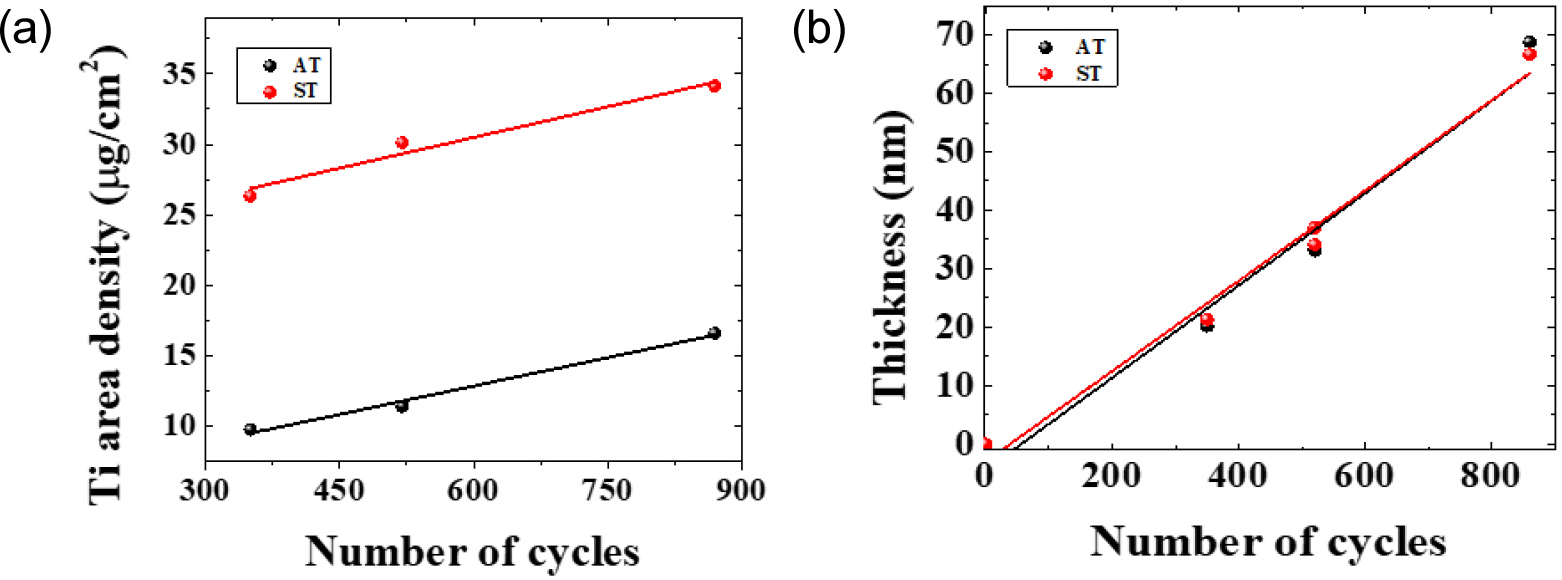

TiO2 유전층은 TiCl4와 O2를 이용한 PEALD로 사이클 수에 따라 증착되었으며, Fig. 3(a)는 박막 샘플들의 XRF 분석 결과이다. ALD 사이클 수가 증가할수록 Ti의 면밀도가 증가하는 경향을 보였으며, AT 샘플들보다 ST 샘플들의 Ti 면밀도 값이 높은 이유는 스퍼터로 증착된 ST 기판의 TiN 두께가 더 두껍기 때문이다. XRF 분석에서 AT와 ST 샘플의 기울기는 각각 0.0134, 0.0145 µg/cm2・cycle로 두 기판 간 큰 차이가 없음을 확인하였다. Fig. 3(b)는 SEM으로 확인한 TiO2 박막의 두께로, 사이클당 증착률(growth-per-cycle, GPC)을 나타내었다. 증착 두께를 확인하였을 때, TiO2 박막이 ALD 공정으로 균일하게 증착되었음을 확인할 수 있다. TiO2 GPC는 AT 기판과 ST 기판에서 각각 0.079, 0.077 nm/cycle로 기판 종류에 따른 유의미한 GPC 차이는 관찰되지 않았다. 이러한 XRF 및 SEM 결과는 TiO2 박막 두께가 증착 사이클 수에 비례하여 성공적으로 제어되었으며, 서로 다른 방법으로 형성된 동일한 기판 물질 위에 TiO2를 증착한 경우에도, 두 조건에서 유사한 성장률을 보여 TiO2 박막의 성장률은 기판 형성 방법에 크게 의존하지 않는 것으로 보인다.

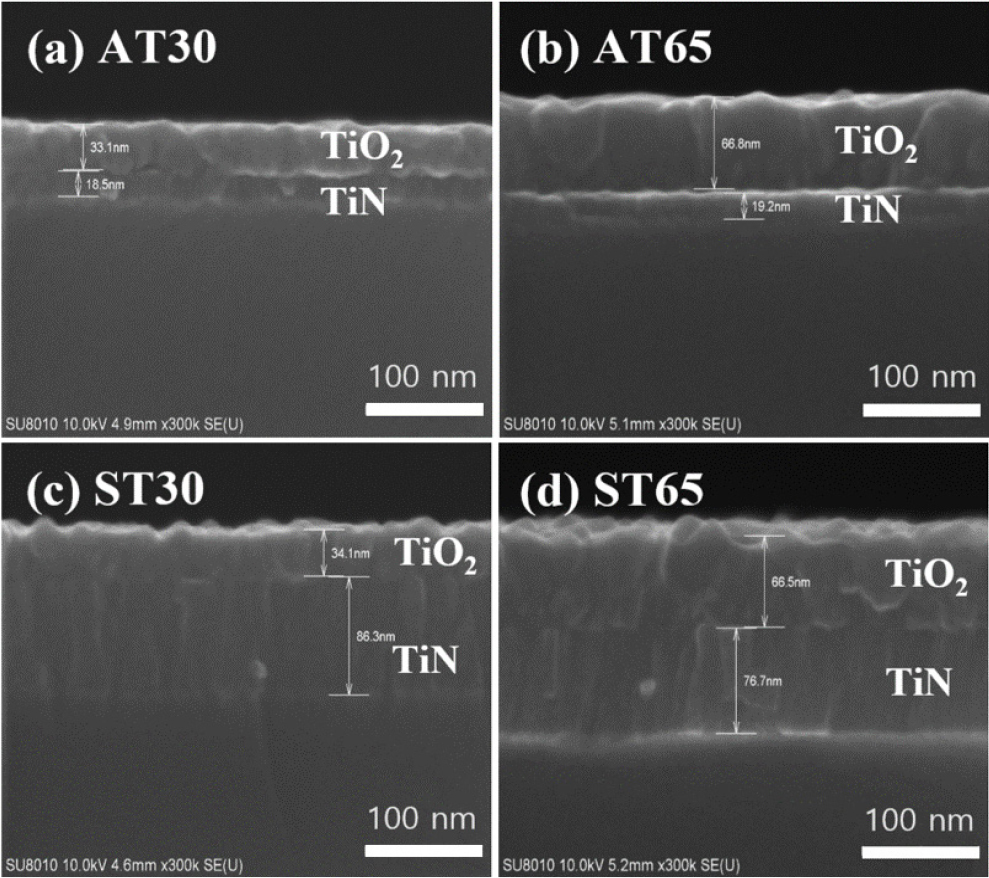

Fig. 4는 TiN과 TiO2 박막의 두께를 확인한 HR-FESEM 이미지이다. SEM 이미지를 통해 증착된 TiN, TiO2 박막이 균일하게 증착되었음을 확인하였고 AT30, AT65, ST30, ST65 샘플의 TiO2 두께는 각각 33 nm, 67 nm, 34 nm, 67 nm로 확인되었다. 또한, AT 샘플의 TiN 두께는 약 20 nm, ST 샘플의 TiN 두께는 약 80 nm의 예상된 두께로 확인되었다.

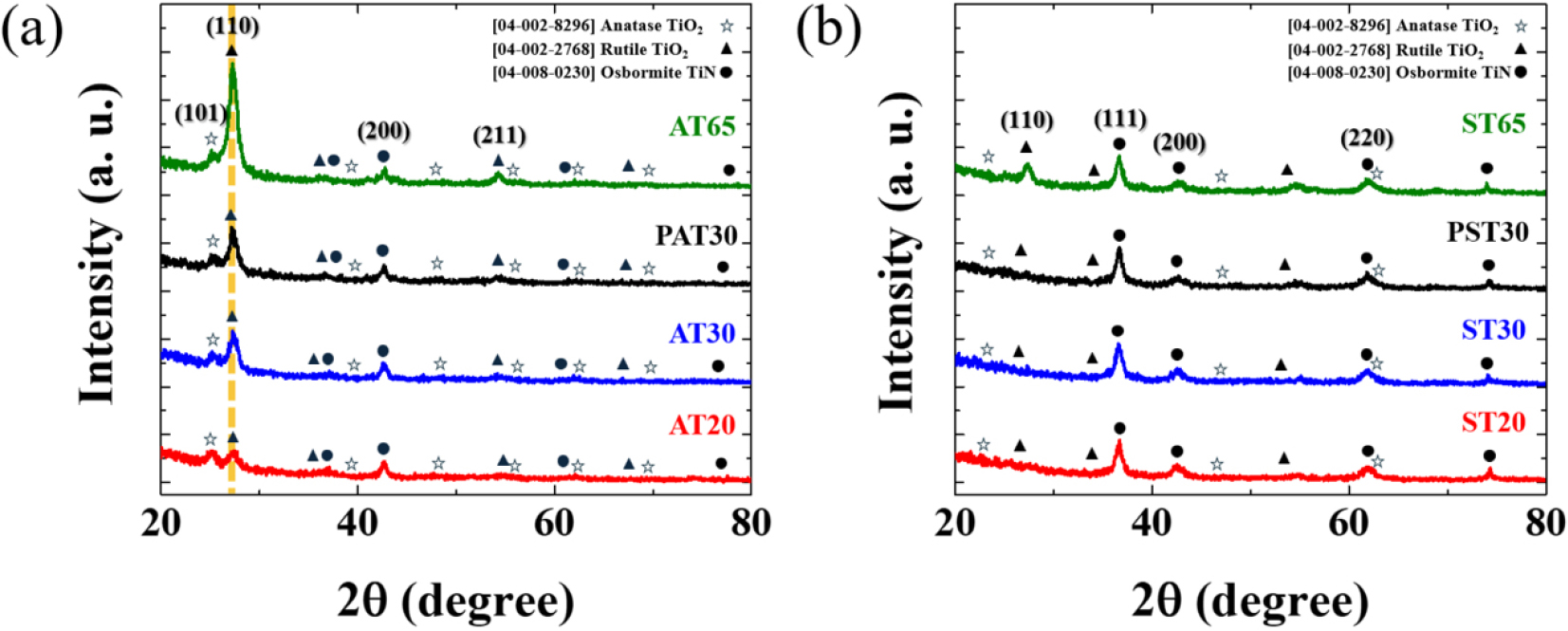

Fig. 5는 8개 샘플의 TiO2 박막의 결정성을 비교한 GIXRD 패턴 데이터로, Fig. 5(a)는 AT 샘플, Fig. 5(b)는 ST 샘플의 결과를 보여준다. XRD 피크 분석 결과, 전체 샘플에서 가장 우세한 회절 피크는 약 27.24° 부근에 위치한 rutile TiO2 (110)면으로 확인되었다. 이외에도 anatase TiO2 (101), osbornite TiN (111), osbornite TiN (200)면에 해당하는 회절 피크들이 각각 25.12°, 36.68°, 42.76° 및 그 인접 각도 영역에서 관찰되었다. 또한, 피크 분석 결과, 모든 샘플에서 rutile TiO2 상과 anatase TiO2 상, 그리고 TiN의 osbornite 상이 동시에 존재함을 확인할 수 있었다. AT 샘플의 경우, TiO2 박막은 주로 rutile 상으로 성장하였으며, rutile 상에 해당하는 회절 피크들이 매우 높은 강도로 관찰되었다. 이는 AT 공정 조건하에서 결정성이 우수한 TiO2 박막이 형성되었으며, 해당 공정 조건이 rutile 상의 형성 및 결정립 성장을 효과적으로 촉진하였음을 의미한다. 특히, rutile TiO2 (110) 및 (211) 회절 피크의 강도가 ALD cycle 수 증가에 따라 점진적으로 증가하는 경향을 보였다. 이는 ALD 사이클 수 증가에 따른 박막 두께 증가와 함께, 반복적인 열 및 O2 플라즈마 노출로 인해 결정성이 지속적으로 향상된 결과로 해석된다. 반면, ST 샘플에서는 AT 샘플에 비해 전반적으로 TiO2 회절 피크 강도가 감소하여 상대적으로 낮은 결정성을 나타내었다. Anatase 상과 rutile 상 모두 뚜렷한 회절 피크로 관찰되지 않았으며, TiN의 osbornite (111) 면이 가장 우세한 회절 피크로 확인되었다. 다만, 박막 두께가 65 nm로 증가한 ST65 샘플에서는 상대적으로 강한 rutile 상의 피크가 관찰되었다. 이는 박막 두께 증가에 따라 상전이가 발생했을 가능성을 의미한다. 비교적 낮은 온도에서 형성되는 anatase 상은 고온에서 rutile 상으로 상전이되는 구조적 불안정성을 지니므로, 장시간 ALD 공정을 거친 ST65 샘플에서는 반복적인 열 노출에 의해 내부 구조 변화 및 상전이가 발생하였을 가능성이 존재한다.

TiN 기판의 피크를 비교한 결과, AT 샘플에서는 (200)면이 우세하게 관찰된 반면, ST 샘플에서는 (111), (220), (200)면이 순차적으로 약한 강도로 관찰되었다. 일반적으로 (111)면은 박막 결정면 중 표면에너지가 가장 낮고 원자 충진도가 높아 열역학적으로 가장 안정하며, 성장과정에서 우선적으로 형성되는 결정면으로 알려져 있다.21,22) 지금까지 TiN 박막의 우선배향은 가스 조성, 가스 압력, 증착 속도, 이온/원자 플럭스 비율 등 다양한 공정 변수에 의해 결정되며, 이에 따라 문헌 간 상충되는 결과가 보고되어 왔다.21) 그중 Yan 등의 연구에 따르면, TiN 박막의 우선배향 변화는 표면에너지와 변형에너지(strain energy) 간의 경쟁에 의해 결정된다.22) FCC 구조를 갖는 TiN 결정에서 (111)면은 영률(Young’s modulus)의 이방성으로 인해 변형에너지가 가장 낮은 반면, (200)면은 표면에너지가 가장 낮은 결정면으로 알려져 있다. 증착 속도가 높을 경우, 고에너지 상태의 다수의 핵(nuclei)이 동시에 생성되면서 박막 내부에 비교적 큰 내부 응력(internal stress)이 형성된다. 이에 따라 고온 또는 스퍼터링 방법으로 형성된 TiN 박막은 변형에너지를 완화하고 박막의 전체 에너지를 최소화하기 위해 (111)면 방향으로 우선 성장하게 된다. 반대로, 저온이나 ALD와 같이 증착 속도가 낮은 경우에는 변형에너지보다 표면에너지가 더 지배적인 요소로 작용하게 되며, 그 결과 표면에너지가 가장 낮은 (200)면의 우선배향이 나타난다.22)

다음으로 XRD 데이터를 이용하여 격자 부정합(lattice mismatch)을 계산하였다. 가장 우세한 TiO2와 TiN 회절 피크를 기준으로 계산한 결과, AT65와 ST65의 격자 부정합 값은 각각 4.66 %, 6.15 %로 확인되었다. 하지만 앞서 언급한 바와 같이, ST 샘플 중 ST65 샘플에서만 rutile 상이 우세하게 관찰되었으며, 그 외 ST 샘플들에서는 rutile과 anatase 상이 공존하되 특정 상이 지배적으로 형성되지는 않았다. 다만, 회절 피크의 상대 강도를 비교한 결과 anatase 상이 매우 소폭 우세한 경향을 보였다. 이러한 상 분포를 고려하여 계산한 ST30 샘플의 격자 부정합 값은 약 36.76 %로 확인되었다. 이를 통해, AT 샘플들이 ST 샘플들에 비해 TiO2 박막과 TiN 하부 전극 간의 격자 정합성과 계면 결합력이 더 우수할 것으로 판단된다.

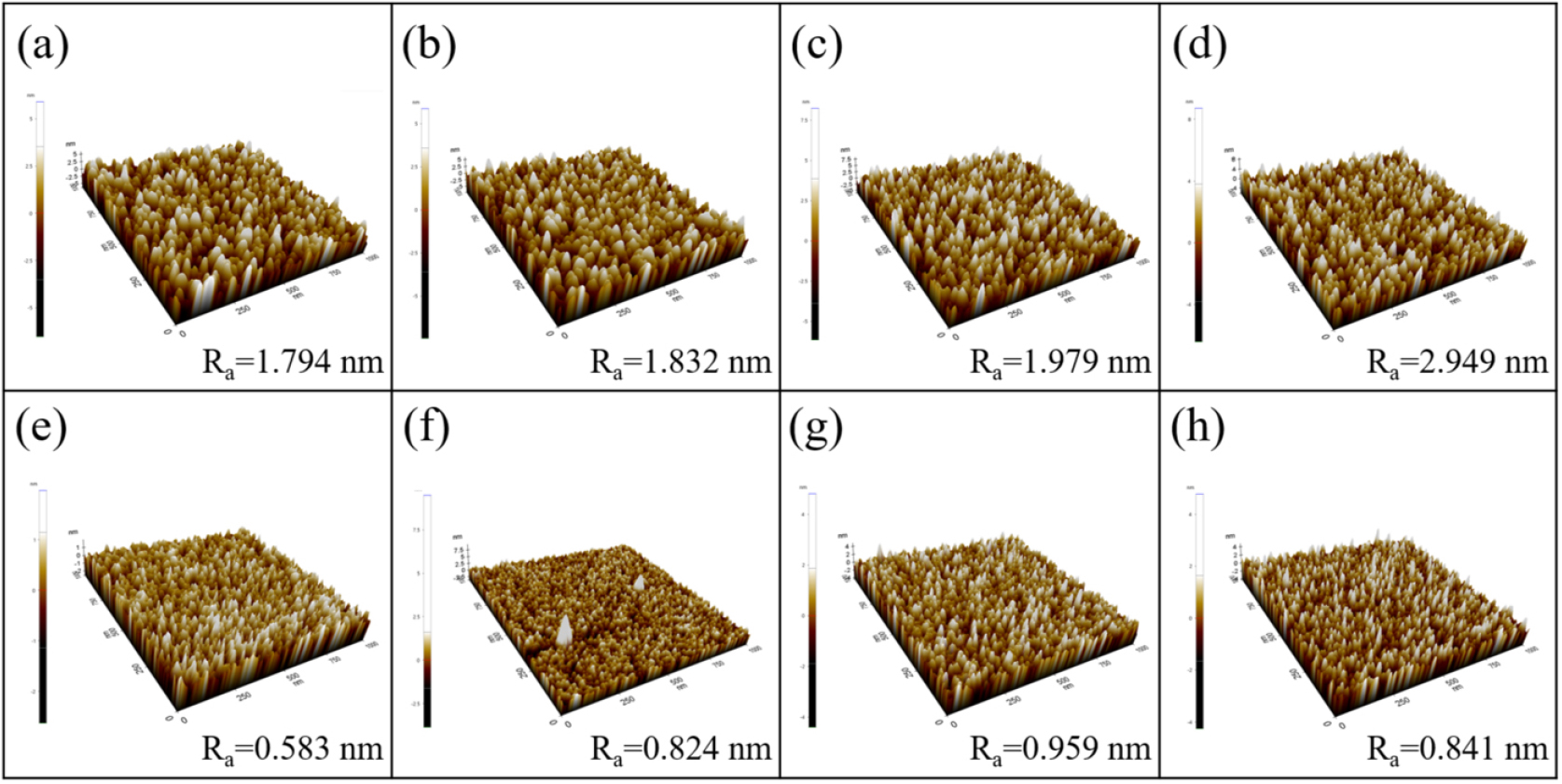

Fig. 6은 AFM 분석을 통해 각 샘플의 표면 모폴로지와 함께 샘플의 RMS 거칠기(Ra) 값도 표시하였다. 30 nm의 TiO2 두께를 가지는 샘플들의 플라즈마 처리 전후의 거칠기를 분석하였고, AFM 분석은 두 가지 조건에서 수행되었다. 첫 번째는 유전층을 형성하지 않은 TiN 기판 자체의 표면의 거칠기를 측정한 경우[Fig. 6(a-d)]이며, 두 번째는 TiN 기판 위에 TiO2 유전층을 증착한 TiO2/TiN 구조에서 TiO2 표면의 거칠기를 측정한 경우[Fig. 6(e-h)]이다. Fig. 6(a, c, e, g) 샘플은 플라즈마 처리 전, Fig. 6(b, d, f, h)는 플라즈마 처리 후의 거칠기를 나타낸다. 첫 번째 경우에서는 우선, 플라즈마 처리 전, AT 기판이 ST 기판보다 거칠기가 더 낮다. 그 이유는 PVD 방식과 비교했을 때 PEALD 공정은 더 치밀하고 균일한 박막 형성이 가능하여 우수한 표면 평탄도를 확보할 수 있기 때문이다. 하지만, 플라즈마 처리를 진행한 PAT 기판은 비교적 평탄한 표면을 가진 AT 보다 거칠기가 증가하게 되었다. 반면, ST 기판은 초기 표면이 상대적으로 거칠었으나, 플라즈마 처리를 진행한 PST 기판에서는 거칠기가 감소하는 경향을 보였다. 이러한 결과는 공정 방식 및 플라즈마 처리 조건이 TiN 박막의 표면 모폴로지에 직접적인 영향을 미침을 나타낸다. 두 번째 경우에서는 TiO2 유전막을 증착한 PAT30과 PST30 모두 AT와 ST보다 더 높은 거칠기 값이 확인되었다. 이는 TiO2 박막 형성 후에는 최상부 거칠기가 TiN 하부 전극보다 TiO2의 성장 균일성에 의해 영향을 받을 가능성을 시사한다. 이 외에도 두께별 TiO2 유전층의 AFM 측정에서는 두께가 증가함에 따라 ALD 공정 중 온도 노출 시간이 길어져 결정립 크기가 증가하고, 이에 따라 표면 거칠기가 함께 증가하는 경향을 보였다.

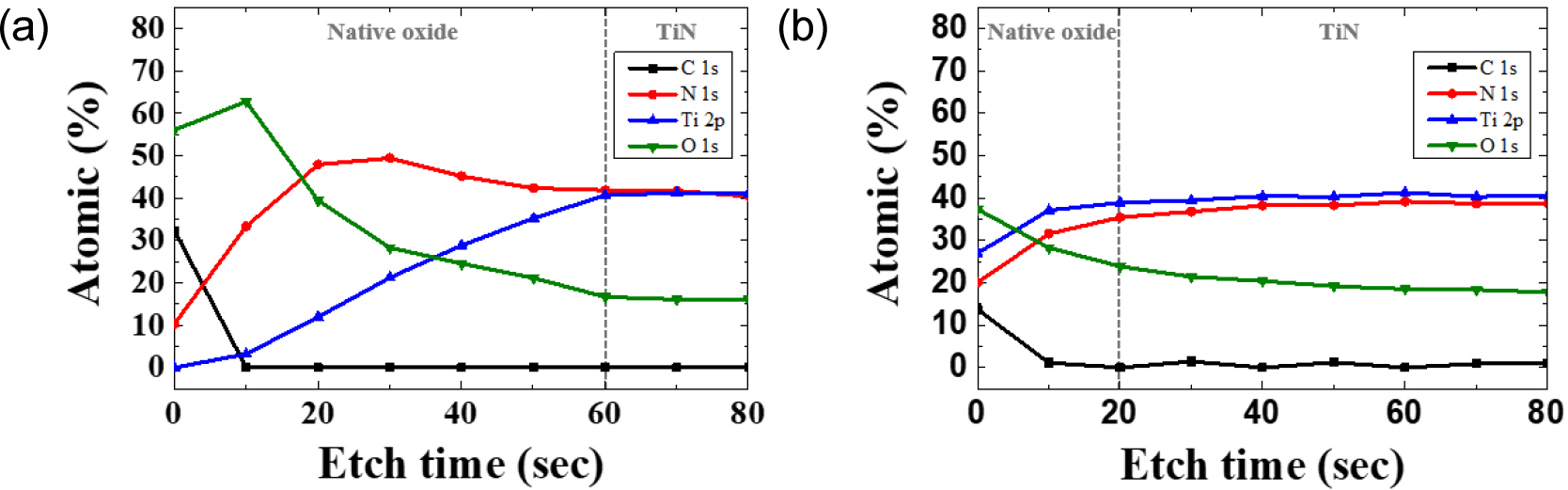

Fig. 7은 AT와 PAT 샘플의 XPS depth profile 분석을 통해 TiN 기판의 플라즈마 처리 전후의 TiN 표면의 성분 변화를 정량적으로 비교하였다. TiN 하부 전극은 공기 노출 과정에서 불균일하고 결함 밀도가 높은 자연산화막을 형성할 수 있으며, 이로 인해 계면 인근에 다수의 산소 공공, 구조적 불완전성 및 전하 트랩이 존재할 가능성이 있다.23) 이때, 아르곤 플라즈마 처리를 진행한 PAT 샘플은 AT 샘플에 비해 표면의 자연산화막과 탄소 등 기타 불순물 농도가 유의미하게 감소하였다. 이는 TiN 표면의 세정 및 활성화 효과를 명확히 보여준다. 불활성 기체로 형성한 아르곤 플라즈마는 물리적 스퍼터링 효과를 통해 표면 결합의 부분적인 재구성이 일어나 표면 반응성이 증가하는 표면 활성화 효과를 유도한다.24) 또한, 표면 활성화뿐만 아니라 표면에 흡착된 오염 물질 제거, 결함 구조 변화 및 표면 에너지 향상을 유도하는 것으로 알려져 있다. 이러한 특성으로 인해 아르곤 플라즈마 처리는 유전막의 무결성 및 계면 결합 특성을 개선하는 데 기여할 수 있다.25,26,27,28) 특히, 이러한 표면 클리닝 효과는 후속 TiO2 증착 시 초기 핵 생성 밀도를 높여 박막의 균일한 성장에 기여하며, 동시에 TiO2 유전층과의 계면 결합을 향상시켜 전기적 접촉 저항을 감소시키는 데 기여할 수 있다.24) 자연 산화막 등 불필요한 계면층은 전기적 특성을 저하시킬 뿐만 아니라 메모리 소자의 신뢰성에도 큰 영향을 미친다.27) 한편, Chin 등의 연구에 따르면, 고유 트랩(intrinsic trap)은 자연 산화막과 관련이 있으며, 이러한 자연 산화막의 존재는 상부에 형성되는 유전막의 신뢰성을 저하시킨다고 보고되었다.29)

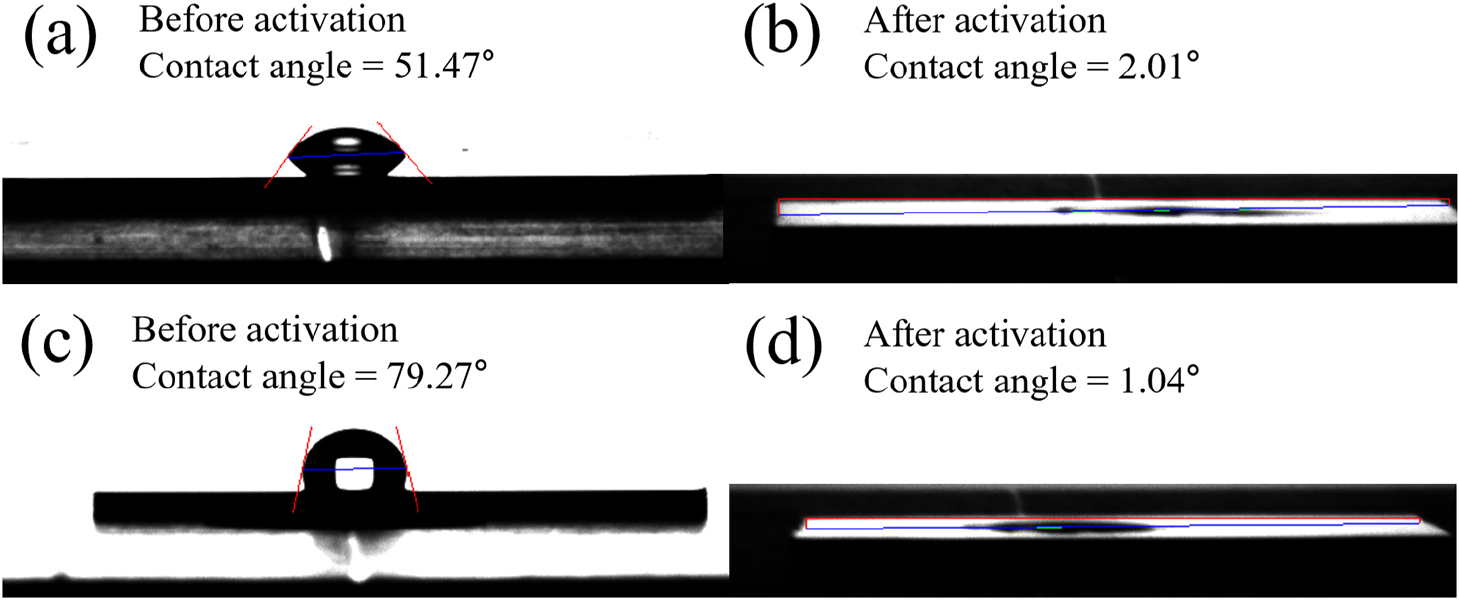

Fig. 8은 TiN 표면의 접촉각(water contact angle)을 측정한 이미지이다. 플라즈마 처리 전 AT와 ST의 접촉각은 각각 51.47°, 79.27°로 측정되었으나, 플라즈마 처리 후 PAT와 PST의 접촉각은 각각 2.01°, 1.04°로 현저히 감소하였다. 이러한 큰 접촉각 감소는 표면 에너지 증가에 따른 TiN 기판의 친수성 향상을 의미한다. Huang 등의 연구에 따르면, 아르곤 플라즈마 처리로 친수성이 향상된 표면은 화학적 활성도를 증가시켜 계면 결합 형성을 촉진하는 동시에, ALD 공정 중 전구체의 흡착 반응과 핵 생성을 촉진시켜 보다 균일한 박막 성장을 유도하는 것으로 알려져 있다.26) 또한, 결함 상태의 형성을 효과적으로 억제하는 효과 역시 확인되었다. Yang 등의 연구는 플라즈마 클리닝으로 접촉각이 80° 이상에서 10° 이하로 줄어 친수성이 매우 향상된 경우, 계면 접착력이 유의미하게 증가함을 보고하였다.28) 따라서 플라즈마 처리된 TiN 표면은 TiO2 유전층의 증착 품질을 개선하며, 이는 계면 결함 밀도 감소 및 전기적 신뢰성 향상으로 이어질 수 있다. 이러한 결과는 표면 플라즈마 개질 공정이 금속/유전체 계면 특성 제어에 효과적인 방법임을 시사한다.

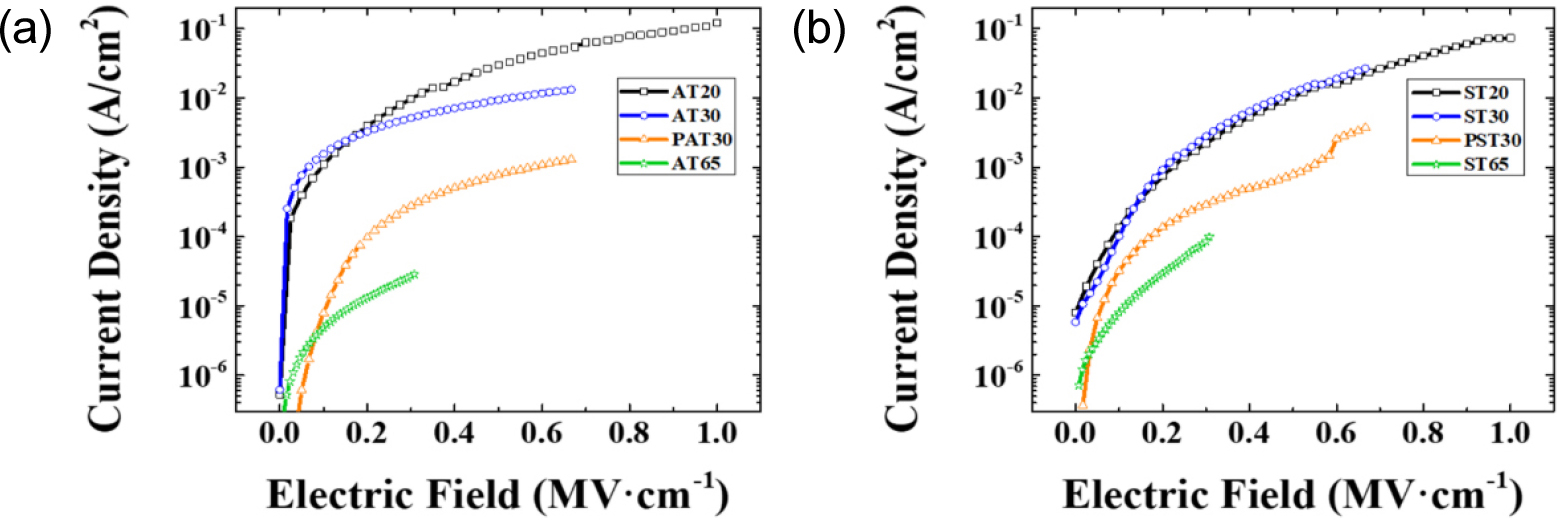

다음으로 Pt/TiO2/TiN 커패시터 소자의 전기적 특성을 평가하였다. Fig. 9는 일반적인 DRAM 소자의 작동 전압 범위에서 측정한 커패시터의 전류밀도-전기장(current density-electric field, J-E) 특성을 나타내며, 이를 통해 각 샘플의 누설전류 특성을 비교 분석하였다. Fig. 9(a)와 (b)는 각각 AT 및 ST 샘플의 J-E 특성을 나타낸다. J-E 특성 분석 결과, AT와 ST 샘플 모두에서 유전층 두께가 두꺼워질수록 누설전류가 감소하는 경향이 확인되었다. 이는 유전층 두께가 증가함에 따라 동일한 인가 전압에서 유전층 내부전기장의 세기가 감소하고, 그에 따라 전자의 터널링 확률이 억제되기 때문으로 해석된다.24) 다만, ST20과 ST30 샘플의 경우 두께 증가에 따른 누설전류 변화가 상대적으로 크지 않아, 두께 효과가 뚜렷하게 구분되지는 않았다. 한편, 동일한 두께 조건에서 AT 샘플들은 ST 샘플들에 비해 전반적으로 낮은 누설전류 특성을 나타냈다. 이는 XRD 분석으로 확인된 rutile TiO2와 TiN 사이의 격자 부정합이 AT 샘플들에서 상대적으로 작아, 계면 결함 밀도가 감소했기 때문으로 판단된다. 감소된 계면 결함 밀도는 전하 이동에 기여하는 누설경로를 억제하여 누설전류 특성 개선에 기여한 것으로 해석된다.30,31) 또한, AT 및 ST 샘플 모두 30 nm의 같은 두께에서 아르곤 플라즈마 처리 이후 누설전류가 감소하였다. 이는 XPS depth profile 분석 및 접촉각 측정 결과에서 확인된 바와 같이, 아르곤 플라즈마 처리에 의해 하부 전극 표면에 존재하던 자연산화막 및 흡착 오염물이 제거되어 TiO2/TiN 계면의 균질성과 안정성이 향상되었기 때문으로 해석된다. 산화막 내 결함은 트랩 사이트로 작용하여 국부적인 전계 집중을 유발하거나 전하 이동 경로를 형성함으로써, 누설전류 증가의 주요 원인으로 작용할 수 있다. 플라즈마 처리로 활성화된 하부 전극 표면은 이후 증착되는 TiO2 유전층과의 계면에서 보다 균일한 결합 형성을 가능하게 하며, 그 결과 계면의 전기적 불균일성과 유효 트랩 밀도를 감소시키는 데 기여한다. 이러한 계면 품질 개선은 산화막 결함 기인 누설전류 경로를 억제하여 누설전류 특성 향상으로 이어진 것으로 판단된다. Chin 등은 자연 산화막이 잔존할 경우, 0.5 V 이하의 저전압 영역에서 게이트 누설전류가 증가함을 보고하였다. 또한, 고유 트랩이 공정 의존적이며, 특히 자연 산화막의 존재와 밀접하게 연관되어 있음을 시사하였다.29)

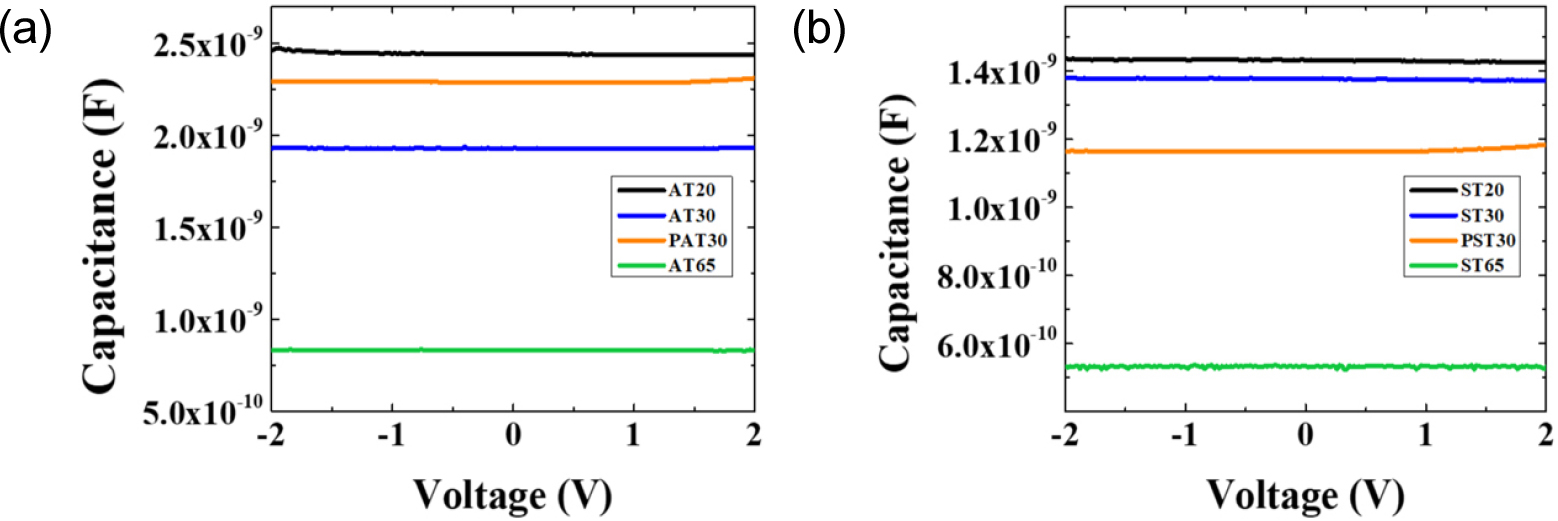

Fig. 10은 제작된 TiO2 박막의 유전층 두께에 따른 C-V 특성을 나타내었다. 유전층 두께가 증가함에 따라 정전용량 값이 감소하는 경향을 보였으며, 이는 평행한 커패시터 모델에서 정전용량이 유전층 두께에 반비례한다는 이론적 관계와 일치한다. 또한, AT 샘플들이 ST 샘플들보다 전반적으로 더 높은 정전용량 값이 확인되었다. 이러한 차이는 앞서 수행한 XRD 분석에서 확인된 결정상 차이에 기인하는 것으로 판단된다. AT 샘플들에서 유전상수가 큰 rutile 상의 TiO2가 우세하게 형성된 반면, ST 샘플에서는 유전상수가 상대적으로 작은 anatase 상이 주로 관찰되었다. 따라서, rutile 상의 비율 증가가 AT 샘플의 정전용량 향상에 기여한 것으로 해석된다. 아르곤 플라즈마 처리 이후에는 AT 샘플과 ST 샘플에서 상반된 정전용량 변화가 나타났다. AT 샘플의 경우, 정전용량이 증가한 반면 ST 샘플에서는 감소하는 경향을 보였다. 이는 AFM을 통해 확인된 표면 거칠기 변화와 관련이 있는 것으로 판단된다. AT 샘플에서는 플라즈마 처리로 인해 표면 거칠기가 증가하면서 실질적인 전극-유전층 접촉 면적이 확대되었고, 이에 따라 유효 정전용량이 증가하였다. 반면, ST 샘플의 경우 플라즈마 처리 후 표면이 상대적으로 평탄화되면서 유효 접촉 면적이 감소하였고, 그 결과 정전용량 값이 약간 감소한 것으로 해석된다. 유전상수는 식을 이용하여 계산하였고, 그 계산 결과는 Table 1에 정리하였다. 여기서 C는 C-V 측정을 통해 얻은 정전용량, t는 유전막의 물리적 두께, ε0는 진공 유전율, A는 커패시터 면적을 의미한다. 계산에 사용된 면적 A는 지름 약 316 µm의 원형 전극 면적에 해당하며, 이는 약 7.84 × 10-4 cm2이다. 또한, 본 연구에서는 이상적인 MIM 커패시터 모델을 가정하였으며, 이에 따라 직렬저항 효과는 고려하지 않았다. 전반적으로 AT 샘플들이 ST 샘플들에 비해 더 큰 유전상수를 나타냈으며, 특히 PAT30 샘플은 약 98의 유전상수를 보여 가장 우수한 특성을 나타냈다. 이는 XRD 분석에서 관찰된 rutile TiO2 (110) 회절 피크가 뚜렷하게 관찰된 결과와 잘 부합하며, 정전용량 값 증가와도 일관된 경향을 보인다. 이러한 결과로부터 rutile 상이 우세한 결정 구조를 가질수록 유전특성이 향상됨을 확인할 수 있다. 또한, AT와 ST 샘플들 모두 계산된 유전상수는 박막 두께가 증가함에 따라 초기에는 증가하는 경향을 보였으며, 일정 두께 증가 이후에는 소폭 감소하는 경향이 관찰되었다. 이러한 거동은 박막 두께 증가에 따라 금속/유전체 계면의 dead layer의 영향이 완화되는 한편, 더 두꺼운 조건에서는 응력 및 결함 형성과 같은 구조적 요인에 기인한 결과로 해석된다.27)

Table 1.

Dielectric constants of samples.

| Sample | AT20 | AT30 | PAT30 | AT65 |

| Dielectric constant | 70 | 83 | 98 | 77 |

| Sample | ST20 | ST30 | PST30 | ST65 |

| Dielectric constant | 41 | 59 | 50 | 49 |

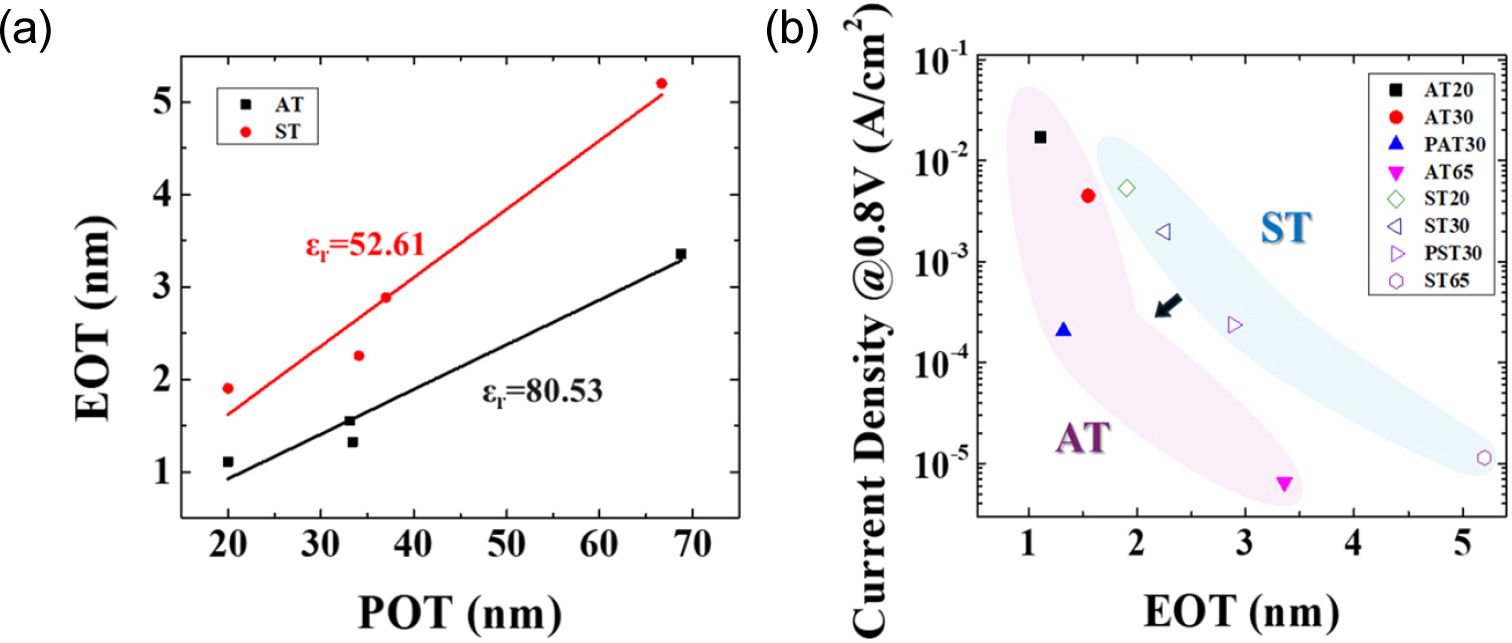

커패시터의 활용 가능성을 확인하기 위해 Fig. 11(a)에 EOT - 물리적 두께(physical oxide thickness, POT) 그래프를 나타내었다. EOT 값은 식을 이용하여 계산하였다. EOT-POT 그래프의 기울기인 유전상수를 비교한 결과, AT 샘플들의 기울기가 ST 샘플의 기울기보다 낮게 나타나 높은 유전율을 보였고 앞선 결과와 동일한 경향을 확인하였다. Fig. 11(b)은 0.8 V 전압 인가 조건에서 EOT와 누설전류 밀도 간의 관계를 나타낸 그래프이다. 일반적으로 EOT 값이 작고 누설전류 밀도가 낮을수록 우수한 커패시터 소자로 평가된다. 해당 그래프에서 PAT30 샘플은 EOT와 누설전류 밀도 모두에서 상대적으로 낮은 값을 동시에 나타내며, EOT-누설전류 특성의 트레이드-오프 관점에서 가장 우수한 특성을 보였다. 이러한 특성 향상은 rutile 상의 형성과 함께 플라즈마 처리에 의해 하부 전극 표면의 클리닝 및 활성화 효과에 기인한 것으로 판단된다. 플라즈마 처리 과정에서 하부 전극 표면이 활성화되었으며, 이에 따라 이후 증착된 TiO2 박막과의 계면 결합력이 향상되었다.32) 그 결과, 보다 균일하고 치밀한 박막 형성이 가능해 졌으며, 이로 인해 정전용량 및 유전상수 증가 등 유전특성 향상으로 이어진 것으로 판단된다.

4. 결 론

본 연구에서는 TiN 하부 전극의 증착 방식(PEALD 및 스퍼터), 아르곤 플라즈마 전처리 유무, 그리고 TiO2 유전층 두께에 따른 TiO2 유전막의 구조적・전기적 특성 변화를 분석하였다. 특히, 높은 유전상수를 갖는 rutile TiO2상의 형성과 누설전류 감소를 위해 하부 전극과 유전막 사이의 계면 특성을 제어하고자 하였다. PEALD-TiN 하부 전극과 sputter-TiN 하부 전극을 적용한 커패시터 소자의 특성을 비교한 결과, 전체적으로 PEALD-TiN 적용 커패시터가 더 낮은 누설전류와 더 높은 정전용량 값을 나타냈다. 또한, XRD 분석 결과, PEALD-TiN 하부 전극과 그 위에 형성된 TiO2 박막 간의 격자 불일치도가 sputter-TiN 하부 전극보다 상대적으로 낮아 rutile 상의 TiO2 형성이 가능함을 확인하였다. 또한, TiN 하부 전극에 아르곤 플라즈마 전처리를 적용한 결과, TiN 표면의 자연 산화막이 효과적으로 제거되고 표면 에너지가 증가하여 TiO2 박막의 성장 환경이 개선됨을 확인하였다. 이러한 계면 특성 향상은 TiO2 박막의 결합력 향상과 함께 누설전류 감소로 이어졌다. 이를 통해 하부 전극의 결정 구조와 계면 상태가 TiO2 결정상 형성에 중요한 영향을 미친다는 점을 확인하였다. 전기적 특성 분석 결과, 아르곤 플라즈마 전처리를 적용한 PEALD TiN 하부 전극을 사용한 샘플에서 최대 98의 높은 유전상수와 함께 약 1.3 nm 수준의 EOT를 확인하였으며, 동시에 누설전류 특성 또한 효과적으로 억제되었다. 본 연구는 하부 전극 증착 방식과 비활성 스퍼터링 효과를 활용한 아르곤 플라즈마 전처리를 통해 TiN/TiO2 계면 특성을 제어함으로써, rutile TiO2 기반 고유전막에서 EOT 감소와 누설전류 억제를 동시에 달성할 수 있음을 입증하였다. 이러한 결과는 차세대 고유전막 기반 소자 응용에 있어 활용 가능성을 보여준다.