1. 서 론

고온에서도 안정적으로 작동이 요구되는 고전력(high power), 고주파수(high frequency) 반도체 수요의 증가에 따라 고온에서 반도체 패키지(package)의 높은 신뢰성이 요구되고 있다.1,2) Backside metallization은 제조된 반도체 칩(chip) 또는 다이(die)를 리드프레임(lead frame)에 접합하는 공정인 다이 본딩(die bonding)을 실시하기 위하여 웨이퍼 후면(backside)에 다층의 박막을 형성하는 기술로서 현재 반도체 제조 공정에 일반적으로 사용되고 있는 방법이다. 칩과 리드프레임 간 접합 면적이 넓기 때문에 오믹 접합(ohmic contact), 전기 전도도(electrical conductivity), 열 방출(heat dissipation) 측면에서 매우 우수한 특성을 지니고 있다.3) Backside metal (BSM)층은 기본적으로 여러 기능(adhesion, diffusion barrier, solder, oxidation protection)을 하는 다층 박막으로 형성되어 있으며, 웨이퍼와 리드프레임 사이에서 안정한 접합 계면을 형성하기 위해서 솔더(solder)층의 재료가 매우 중요하다.4) 일반적으로 Au 계열 합금이 솔더 재료로서 사용되고 있으나 제조 비용 측면에서 매우 불리하기 때문에 현재까지 이를 대체하고자 하는 다양한 재료를 개발하기 위한 연구가 수행되고 있다.5.6.7.8.9.10.11.12)

본 연구진은 최근 BSM층의 솔더 물질로서 Sn, Ag를 다층의 박막으로 구성하여 Cu가 도금된 alloy 42 리드프레임에 접합했을 때 20 ms의 매우 빠른 시간에 235 °C의 낮은 온도에서 접합이 가능하고, 계면에서 Ag3Sn, Cu6Sn5, Cu3Sn 금속간화합물(intermetallic compound)을 형성하여 400 °C에서도 재용융(re-melting)이 발생하지 않는 공정을 개발하였으며, 이를 일부 패키지 생산 공정에 적용하였다.13) Sn은 약 232 °C의 낮은 녹는점을 갖고 있기 때문에 낮은 온도에서도 칩과 리드프레임의 접합을 가능하게 한다. Sn을 기반으로 하는 BSM이 적용된 반도체 패키지를 생산할 때 칩을 리드프레임에 전기적으로 연결하기 위하여 다이 본딩 후 와이어 본딩 공정을 실시하게 된다. 와이어 본딩 실시 중 공정온도, 시간 등의 문제가 발생할 경우 다이 본딩을 실시하고 있는 제품은 기존 공정조건과 다른 공정온도에 노출되어 지속적으로 열에너지를 받을 수 있게 된다. 이 때 접합 계면에서 공정조건과 다른 열에너지 노출로 인해 미세구조의 변화가 발생할 수 있으며, 변화에 따른 품질의 저하를 야기할 수 있기 때문에 미세구조 변화 과정을 면밀히 조사하여 제품의 불량을 방지하기 위한 연구가 필요하다.

이러한 이유로 본 연구에서는 Sn-Sb 합금을 BSM의 솔더 층으로 이용하여 그 특성을 평가하였다. Sn의 wetting flow를 향상시키기 위해 1 at% 미만의 Sb를 첨가하여 합금을 제조하였다. 제조 현장에서 발생할 수 있는 설비 오작동에 의한 미세구조 변화를 조사하기 위해 다이 본딩 후 그 온도에서 5분 동안 열처리를 실시하였다. 그 후 다이 본딩 및 와이어 본딩 공정 후 미세구조의 변화를 조사하였다. 마지막으로 각 공정 별로 제작된 샘플의 wetting 특성과 전단 강도를 측정하여 기계적 특성을 평가하였다.

2. 실험 방법

먼저 BSM 층의 증착을 위해 1 % 불산을 이용하여 Si 웨이퍼의 산화물을 제거하였다. 그 후 아세톤, 이소프로필알코올, 증류수를 이용하여 웨이퍼 세척을 실시하였다. 산화물이 제거된 Si 웨이퍼의 후면에 e-beam 증착기(CHA Industries, Mark 50)를 이용하여 Ti (150 nm), Ni (320 nm), Sn-Sb (2,250 nm), Ag (200 nm) 순서로 증착하였으며, 기판 온도는 각각 170 °C, 140 °C, 70 °C, 60 °C로 조절하였다. 금속 박막 증착은 2 × 10-6 Torr가 되었을 때 시작하였으며, 증착 속도는 0.8 nm/s로 모두 동일한 조건에서 수행하였다.

다이 본딩을 하기 위하여 BSM 층이 증착된 Si 웨이퍼를 dicing 장비(Disco dicer, DAD522)를 이용하여 0.51 µm × 0.51 µm 크기의 칩으로 절단하였다. 절단된 Si 칩은 다이 본딩 설비(TSP, KD-530)을 이용하여 2 µm 두께의 Ag가 도금된 Cu 리드프레임에 0.1 N의 힘으로 0.1 s 동안 본딩 공정을 수행하였다. 다이 본딩 온도는 290 °C, 330 °C, 370 °C의 세 조건에서 실시하였다. 리드프레임에 접합된 칩의 항온 열처리를 위해 다이 본딩 후 설비 내에서 다이 본딩 온도를 5분 동안 유지하였다. 그 후 질소 분위기에서 상온으로 냉각을 실시하였다. 와이어 본딩은 동일한 설비에서 수행하였으며 본딩 온도는 260 °C로 설정하였다. Table 1에 각 공정 조건을 나타냈다.

Table 1.

Die bonding and wire bonding conditions used in this study.

| Condition | Die bonding temperature | Heat treatment temperature (time) | Wire bonding temperature |

| A | 330 °C | - | - |

| B | 330 °C | 330 °C (5 min) | - |

| C | 330 °C | - | 260 °C |

Si 웨이퍼에 증착된 BSM 박막 및 다이 본딩 후 계면 구조는 전계방사형 주사전자현미경(field emission scanning electron microscopy, FE-SEM, JEOL, JSM-6500F)을 이용하여 조사하였다. Mapping 및 정량 분석은 FE-SEM에 장착된 energy dispersive X-ray spectroscopy (EDS, QUANTAX EDS for SEM, Bruker)를 이용하였다. 리드프레임에 접합된 칩의 전단 강도는 MIL-STD-883C test method 2019.9에 따라 die shear tester (Rhesca, PTR-1000) 설비를 이용하여 평가하였다. 각 조건 별 30개의 칩을 이용하여 전단 강도를 평가하였다.

3. 결과 및 고찰

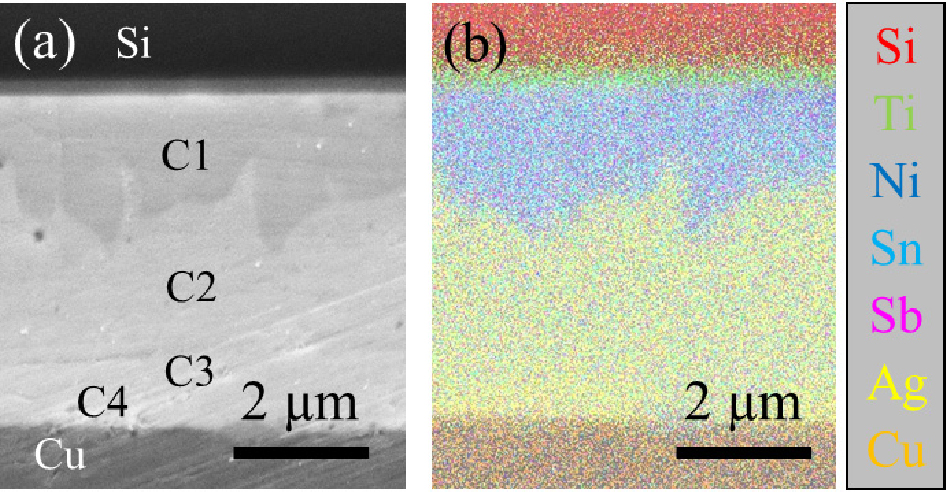

Fig. 1(a)는 다이 본딩 전 웨이퍼 후면에 증착된 Sn-Sb BSM 층의 단면 이미지를 보여준다. EDS mapping 분석 결과 증착된 방막 층은 Ti, Ni, Sn-Sb, Ag로 이루어진 것을 확인할 수 있다[Fig. 1(b)]. Ti 층은 Si 웨이퍼와의 adhesion 향상, Ni 층은 Si 웨이퍼로의 Sn 확산을 방지하는 역할을 하며, 두 금속 층은 매우 균일하게 증착된 것을 확인할 수 있다. SEM 이미지로부터 Ni 층과 Sn-Sb 층 사이에 새로운 층이 형성된 것을 확인할 수 있다. 이 층에 존재하는 원소를 조사하기 위해 EDS 정량 분석을 실시하였으며, Ni와 Sn이 각각 42.1 at%, 57.9 at%의 비율로 존재하는 것으로 확인되었다. Ni과 Sn의 원자비로부터 Ni3Sn4 금속간화합물이 형성되었을 것으로 판단된다. Sn-Sb 증착 후 Ni3Sn4 금속간화합물이 형성되는 이유는 다음과 같다. Sn이 증착될 때 Sn vapor는 높은 열에너지를 지니고 있기 때문에 Ni와 반응하여 Ni3Sn4 금속간화합물이 형성될 수 있다.14,15) 또한, Ni은 상온에서 Sn으로 침입형 확산(interstitial diffusion)이 가능하기 때문에 Ni-Sn 금속간화합물이 형성될 수도 있다. Sn-Sb 증착 후 Ag 층을 증착한 이유는 Sn-Sb의 산화 방지를 통해 다이 본딩 과정에서 접합성을 향상시키기 위한 것이다.

Sn-Sb BSM의 특성을 조사하기 위해 BSM 층이 증착된 반도체 칩을 2 µm의 Ag가 도금된 Cu 리드프레임에 본딩한 뒤 계면의 단면 구조를 Fig. 2에 나타냈다. 330 °C에서 본딩 후 추가적인 열처리를 수행하지 않았을 때 계면에 공극(void)이 형성되지 않은 것으로 확인되었다. EDS mapping 분석을 통해 접합 계면은 주로 두 층으로 구분되는 것을 확인하였다. Si 웨이퍼 부분(위)에는 Ni, Sn, Sb 원소가 분포되어 있고, Cu 리드프레임 부분(아래)에는 Sn, Ag가 주로 분포되어 있다. 계면의 각 영역(A1~A4)의 EDS 정량 분석을 통해 계면에 존재하는 원소의 비율을 조사하였다(Table 2). A1 위치에는 Ni 41.8 at%, Sn 58.2 at%이 검출되는 것으로 보아 Ni3Sn4 금속간화합물이 존재하는 것으로 확인되었다. A2 위치에는 Sn 100 at%로 확인되었다. 본 연구에서 사용한 Sn-Sb 합금에는 Sb가 1 % 미만으로 첨가되어 SEM-EDS 분석의 검출 한계로 인해 정량 분석으로는 나타나지 않았으나 mapping 이미지로부터 Sb 원소가 뚜렷하게 나타났다. A3 위치에는 Sn 25.2 at%, Ag 74.8 at%로 검출되었고, Sn과 Ag의 비율(1:3)로부터 Ag3Sn 금속간화합물이 형성된 것을 알 수 있다. A4 위치(Ag 100 at%)에는 Ag 도금 층이 존재하지만 Sn과의 반응에 의해 두께가 얇아진 것을 알 수 있다.

Table 2.

EDS quantitative analysis of the interface between Si chip and Ag-plated Cu lead frame of condition A (unit: atomic percent).

| Position | Ni | Sn | Ag |

| A1 | 41.8 | 58.2 | - |

| A2 | - | 100 | - |

| A3 | - | 25.2 | 74.8 |

| A4 | - | - | 100 |

Fig. 3과 Table 3은 다이 본딩 후 330 °C에서 5분 동안 항온 열처리를 실시한 후 계면의 단면 구조 및 EDS 정량 분석 결과를 나타냈다. EDS 분석을 통해 B1 위치에는 Ni 43.4 at%, Sn 56.7 at%가 검출되었으며, 추가적인 열처리가 없을 때의 계면과 동일하게 Ni3Sn4가 존재하는 것으로 확인되었다. B2 위치에는 Sn 25.9 at%, Ag 75.1 at%가 검출되어 Ag3Sn 층으로 확인되었고, B3번 위치에는 Ag 97.3 at%, Cu 2.7 at%이 검출되어 Ag 도금 층에 Cu가 미량 확산된 것을 알 수 있다. 5분간의 항온 열처리 후 계면에 순수한 Sn 영역이 존재하지 않는 것으로 확인되었다. 추가적인 열처리에 의해 Sn이 모두 소비되어 Ni3Sn4와 Ag3Sn 금속간화합물이 형성된 것으로 판단된다.

Table 3.

EDS quantitative analysis of the interface between Si chip and Ag-plated Cu lead frame of condition B (unit: atomic percent).

| Position | Ni | Sn | Ag | Cu |

| B1 | 43.3 | 56.7 | - | - |

| B2 | - | 25.9 | 75.1 | - |

| B3 | - | - | 97.3 | 2.7 |

본 논문의 서론에서 설명했듯이 반도체 칩과 리드프레임을 전기적으로 연결하기 위해 다이 본딩(칩과 리드프레임의 접합) 공정 후 와이어 본딩 공정을 수행하게 된다. 와이어 본딩을 실시하는 과정에서 설비에 문제가 발생할 경우 열에너지가 가해지기 때문에 와이어 본딩 후 접합부의 계면 변화를 또한 조사할 필요가 있다. Fig. 4는 다이 본딩 및 와이어 본딩(260 °C) 후 칩과 리드프레임 사이 계면의 단면을 나타냈다. C1 위치는 Ni3Sn4, C2 위치는 Ag3Sn, C3 위치는 (Ag,Cu)3Sn, C4는 Ag 도금 층으로 확인되었다(Table 4).16) EDS 분석을 통해 와이어 본딩 전과 비교했을 Cu가 계면으로 더 확산되어 Ag3Sn의 일부 영역에 (Ag,Cu)3Sn이 존재하는 것을 알 수 있으며, 그 외 큰 변화는 나타나지 않았다. Sn-Sb BSM은 다이 본딩 후 항온 열처리 및 와이어 본딩과 같은 추가적인 열처리 공정에도 불구하고 안정적으로 계면 구조가 유지되는 것을 SEM, EDS를 통해 판단할 수 있다.

Table 4.

EDS quantitative analysis of the interface between Si chip and Ag-plated Cu lead frame of condition C (unit: atomic percent).

| Position | Ni | Sn | Ag | Cu |

| C1 | 43.2 | 56.8 | - | - |

| C2 | - | 25.9 | 75.1 | - |

| C3 | - | 24.8 | 70.9 | 4.3 |

| C4 | - | - | 94.6 | 5.4 |

Fig. 5는 290 °C, 330 °C, 370 °C에서 다이 본딩 및 5분 열처리 후 전단 강도 평가 시험 결과를 보여준다. 모든 조건에서 각 30개 시편을 평가하였다. 5분의 추가 열처리가 없을 때 다이 본딩 온도에 관계없이 약 65 MPa의 전단 강도를 보이고 있다. 5분 열처리 후 본딩 온도 330 °C를 제외하고 열처리 전에 비해 약 3~4 MPa 낮은 값을 나타냈다. 와이어 본딩 후 전단 강도는 평균 78.2 MPa로 다이 본딩 후 측정한 결과보다 10 MPa 이상 높게 나타났다. 본 연구에서 사용된 반도체 패키지에서 요구하는 전단 강도는 6.2 MPa 이상이다. 요구 조건에 비해 Sn-Sb BSM은 약 10배 높은 값을 보이는 것을 알 수 있으며, 계면에 형성된 금속간화합물들에 의한 결과이다.

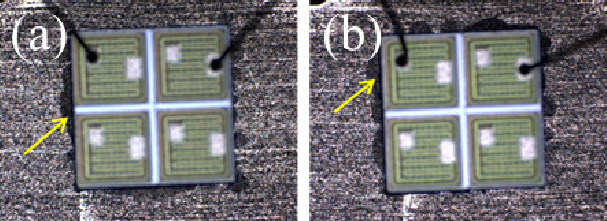

마지막으로 Sn-Sb BSM의 wetting flow를 평가하였으며 그 결과를 Fig. 6에 나타냈다. Fig. 6에 표시된 화살표는 다이 본딩 후 백메탈 물질이 칩 영역 밖으로 흘러나온 것을 보여주는데 이러한 결과는 접합 물질의 wetting 특성이 우수한 것을 보여준다. 높은 비율의 Sb는 접합 재료에 첨가될 경우 본딩 시 wetting 특성을 저하시킬 수 있으나 미량 첨가되었을 경우 반대로 향상시킬 수 있는 특징이 있다. 본 연구에서는 1 % 미만의 Sb를 Sn에 첨가를 통해 본딩 온도에 관계없이 우수한 wetting 특성을 보이는 것이 확인되었다. 결과적으로 Sn-Sb BSM이 반도체 접합 물질로서 우수한 특성을 보여주는 것을 확인할 수 있다. 추가적으로 전기적 특성 및 환경 시험 평가를 통해 본 연구에서 사용한 물질은 제조 공정에 적용될 수 있을 것으로 판단된다.

4. 결 론

본 연구에서는 Sn에 Sb가 미량 첨가된 합금을 BSM의 솔더 재료로 적용하여 다이 본딩을 실시하였으며, 다이 본딩 후 와이어 본딩을 하는 과정에서 열에너지가 가해질 때 변화하는 미세구조를 다이 본딩(A조건), 다이 본딩 후 5분 항온 열처리(B조건), 와이어 본딩(C조건)으로 구분하여 조사하였다. SEM, EDS 분석을 통해 증착된 BSM층 단면을 조사하여 Ni 층과 Sn-Sb 층 사이에 Ni3Sn4 금속간화합물 층이 형성된 것을 확인하였다. 그 후 330 °C에서 BSM 층이 증착된 반도체 칩을 2 µm의 Ag가 도금된 Cu 리드프레임에 접합하여 계면에 Ni3Sn4, Ag3Sn과 Sn이 존재하는 것을 확인하였다. 다이 본딩 후 5분 동안 항온 열처리를 하였을 때 Sn은 모두 소비되어 Ni3Sn4, Ag3Sn이 형성된 것을 알 수 있었다. 이 때 접합 계면으로 Cu의 확산이 시작되며 와이어 본딩 후 더 많은 Cu의 확산이 발생하여 Ag3Sn의 일부 영역에서 (Ag,Cu)3Sn이 형성된 것을 확인하였다. 전단 강도 평가 결과 Sn-Sb 합금은 최대 78.2 MPa의 값이 측정되었으며, 반도체 패키지에 적용하기 위한 최저 조건인 6.2 MPa에 비해 약 12배 이상 높은 값으로 나타났다. 또한, 모든 조건에서 우수한 wetting 특성을 갖는 것으로 확인되었다. 결과적으로 Sn-Sb 합금을 BSM 재료로 이용하면 칩과 리드프레임 계면에서 금속간화합물을 형성하고 우수한 열적 안정성과 높은 전단 강도를 확보할 수 있다. 추가적인 전기적 특성 또는 환경 안정성 평가를 실시하여 본 공정의 신뢰성을 확보할 수 있다면 반도체 패키지 생산 공정에 적용할 수 있을 것으로 판단된다.