1. 서 론

최근 메탈 재질은 수려한 외관 때문에 많은 제조사가 스마트 폰의 케이스로 사용하고 있다. 그러나 메탈 케 이스를 사용하게 되면 충전시 AC전원에 의해 누설전류 가 발생할 가능성이 존재한다. 이러한 누설전류가 신체 와 접촉하게 되면 찌릿찌릿한 불쾌감을 야기할 뿐 아니 라, 심한 경우는 사용자가 감전에 의한 치명상을 입을 수 있다. 적절한 형태의 커패시터를 이용하면 이 현상 을 방지할 수 있으나 이러한 커패시터는 인간의 몸에서 발생하는 정전기에 파괴될 수도 있다는 약점을 가지고 있다.

이와 더불어 스마트폰의 다기능화에 따라 통화 기능의 GSM, DCS 외에 멀티미디어 통신을 위한 LTE, 그리고, 부가기능으로써 WiFi, GPS, 블루투스등 다양한 안테나 가 채용 되고 있으며, 이러한 안테나 특성을 매칭하기 위하여 다양한 값의 세라믹 커패시터가 사용되고 있다. 그 러나 이러한 커패시터도 마찬가지로 정전기에 유입에 의 해 쉽게 파괴되어 매칭이 깨질 가능성이 존재한다.

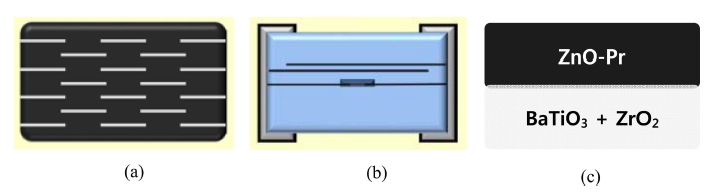

따라서 이러한 감전과 매칭의 문제를 해결하기 위해서 는 ESD 내성을 갖춘 커패시터 소자가 필요하다. 이러 한 소자는 일차적으로 Fig. 1(a)과 같은 구조의 바리스 터로 구현이 가능하다. 그러나 바리스터의 경우 감전을 막기 위하여 바리스터 전압을 340 V까지 올리게 되면 제 한된 유전율로 인하여 2pF 정도의 정전용량 값만을 갖 게 되어 용도가 제한된다. 따라서 Fig. 1(b) 처럼 단일 세라믹 유전체로 만든 커패시터 내부에 gap 방전회로를 구성하는 방법을 고안할 수 있으며 이 방법으로 ESD 내 성을 갖는 다양한 값의 커패시터 소자의 구현이 가능하 다. 그러나 gap 방전 회로는 안정된 방전 특성 구현에 문제가 있어, 민감한 회로의 경우 불안정한 방전 특성 을 보이게 된다. 이러한 문제를 해소하기 위하여 세번 째로 커패시터와 바리스터를 직접 결합하는 Fig. 1(c) 구 조의 소자를 고안할 수 있다. 커패시터와 바리스터의 결 합은 두가지 방법으로 가능하다. 첫번째로 바리스터와 커 패시터를 따로 만들어 접착제로 두 소자를 부착하는 방 법이다. 이 방법으로 우수한 특성을 구현할 수는 있으 나 소자를 각기 따로 제조하여야 하는 점, 접착제를 붙 이면서 여러가지 불량을 야기할 수 있다는 점, 전체적 으로 생산성이 떨어진다는 점 등이 약점으로 지적될 수 있다. 이러한 약점을 상쇄하기 위하여 바리스터와 커패 시터를 동시에 소성하는 방법이 있으나 조성차로 인한 수축률의 차이, 동시 소성시 구성원소의 확산으로 인하 여 바리스터 특성 구현이 어렵다는 난점이 존재한다. 그 러나 커패시터 재료에 적절한 원소를 첨가하여 수축률 을 제어하고 버퍼층을 바리스터와 커패시터 사이에 삽 입하여 소성시 확산을 최소화함으로써 각각의 특성이 이 상적으로 구현된 동시 소성에 의한 단일 소자의 제조가 가능하였다.

2. 실험방법

2.1 접착제를 이용한 바리스터 및 커패시터의 결합

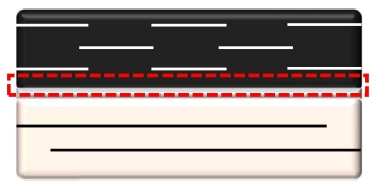

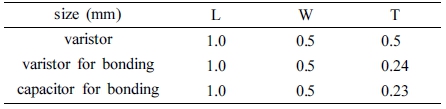

접착제를 이용하여 바리스터와 커패시터를 접합하여 원 칩화 하였다. 바리스터는 기존의 바리스터와 동일한 조 성으로 원하는 바리스터 전압(Vn)값을 구현하기 위해서 는 Fig. 2와 같이 floating 방식의 내부전극을 이용하였 다. floating방식으로 내부전압을 설계하면 유전체층 한층 에 걸리는 전압은 floating 숫자에 따라 1/2, 1/4, 1/6, 1/8으로 줄어드나 정전용량은 1/4, 1/8, 1/12, 1/16 정도 로 줄어 든다. 따라서 정전 용량은 2pF 정도로 한정된 다. 이에 부족한 정전용량 값을 보상해줄 수 있는 커패 시터를 추가적으로 접합해야 하는데, 기존 제품과의 사 이즈는 동일하면서 동등한 성능을 구현하기 위해 Table 1과 같이 칩의 사이즈를 길이와 폭은 같지만 두께는 낮 게 제작하였다. 아래의 표는 기존 제품과 접합용 제품 의 크기를 나타낸다.

Table 1과 같은 사이즈로 만들어진 각각의 칩을 에폭 시 접착제를 이용하여 접합하여 감전보호소자를 만들었 다. 접합부의 도포는 서스 메쉬를 이용한 스크린 인쇄 법으로 진행하였으며, 스크린 선정은 인쇄 면적및 인쇄 레벨링성을 고려하여 325 mesh counter-28um diameter 메쉬를 이용하여 도포하였다.

2.2 동시 소성형

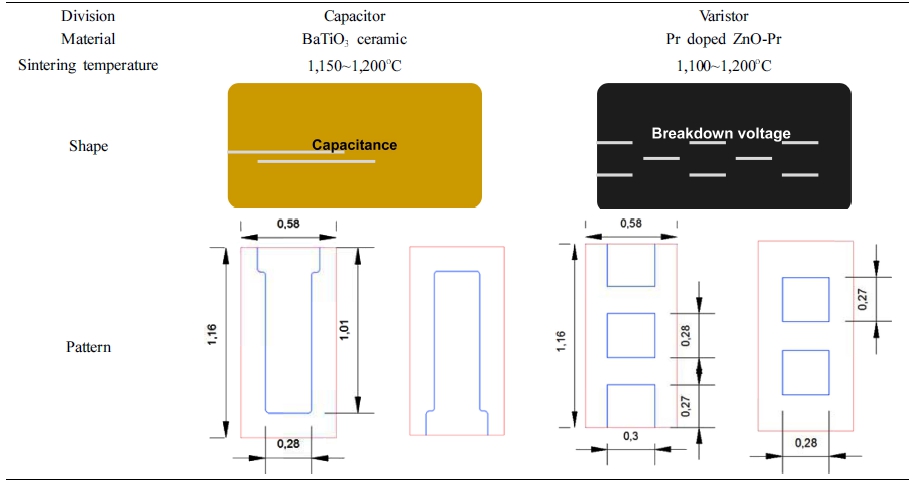

접합제를 이용한 바리스터와 캐패시커의 일체화는 우 수한 특성을 구현할 수 있으나 칩사이즈의 편차, 접착 제의 도포 등에서 여러가지 불량을 야기할 수 있으며 생산성도 떨어진다는 문제점을 내포하고 있다. 이에 본 연구에서는 동시 소성형 이종 접합을 개발하여 문제점 을 해결하고자 한다. 커패시터와 바리스터를 동시 소성 에 의해 제작하기 위한 본 실험의 출발물질로 capacitor 는 BaTiO3를 포함하는 세라믹 재질과 소결조제로 선정 하였으며, 바리스터는 ZnO-Pr계 조성을 그대로 사용하 였다.1-10) 동시 소성의 특성상 유사한 소성온도와 수축율 을 가지는 조성을 선정하기 위해 바리스터의 조성은 고 정하고 커패시터 부의 소성온도와 수축율을 맞추기 위해 유전체와 소결조제의 비율을 바꿔가며 설계를 진행하였 다. 선정한 세라믹 조성은 고온용 세라믹 조성으로 소성 온도는 1,150~1,200 °C이며, 바리스터의 소성온도와 유사 하여 동시소성이 가능할 것으로 판단하였다. Capacitor의 패턴은 Table 2와 같이 병렬 구조로 설계하였으며, 바리 스터의 경우 높은 항복전압을 구현하고 우수한 ESD 내 성을 갖도록 직병렬 구조로 설계하였다. 선정된 BaTiO3 계 세라믹 조성과 ZnO-Pr계 조성에 대해 tape casting 을 통해 각각 39 um, 25 um sheet를 제작하였다. 제작 된 sheet 위에 print screen 공정을 통해 내부전극인 Pd paste를 도포하였다. 설계된 적층조건에 의해 sheet 를 적층 하였으며, 적층 압력은 10 ton/cm2로 진행하였 다. 적층된 sheet는 진공비닐 포장 후 80 °C, 400 kg/ cm2 조건으로 WIP를 진행하였으며, 가로 1.16 mm, 세 로 0.58 mm로 절단하였다. 탈바인더는 280 °C/8 h 진행 후, 1,100 °C/4 h에서 소결하였다. 소결된 시료는 100 Ag paste로 밴드폭 150 um 외부 전극을 형성하여 625 °C/2.5 h 전극 소부 후 특성을 평가하였다. 소성 시 세 라믹의 성분이 바리스터 쪽으로 확산되어 바리스터 특 성이 열화 또는 short 현상을 방지하기 위해 이종 접 합면 사이에 버퍼층을 넣었다. 버퍼층의 주 성분은 반 응성이 낮은 ZrO2을 주성분으로 하고, 소성 후의 수축 률을 세라믹과 바리스터에 맞추기 위하여 ZnO계 글라 스를 치환하여 수축율을 일치시켰다. Fig. 2는 바리스 터와 커패시터 층 사이에 버퍼층이 삽입된 시료의 모 식도 이며, tape casting을 통해 sheet 두께는 35 um로 제작하였다.

2.3 특성측정 및 관찰

2.3.1 전기적 특성(capacitance, breakdown voltage) 측정

전기용량인 커패시턴스는 impedance analyzer(E4990A, KEYSIGHT)를 이용하여 1 MHz에서 측정하였으며, 바리 스터 전압은 source meter(2410, 1,100 V, KEITHLY)를 이용하여 1.0 mA를 인가하여 측정하였다.

2.3.2 유전율 측정

유전율 측정은 impedance analyzer(E4990A, KEYSIGHT) 를 이용하여 1 MHz에서의 커패시턴스를 측정하여 공기 의 유전율을 1로 보고, 시료의 유전율을 계산하는 비유 전율을 구한 것으로 계산식은 (1)과 같다.

여기서 ε0는 진공의 유전율, εr은 재료의 유전율, S는 전 극 교차 면적, d는 유전체 한층 두께, n은 적층 매수를 나타낸다.

3. 결과 및 고찰

3.1 접착제를 이용한 바리스터와 커패시터 접합 칩 의 특성

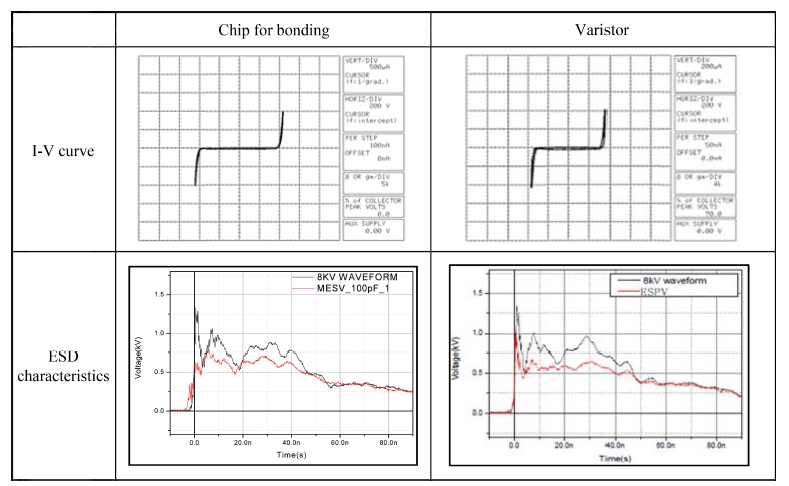

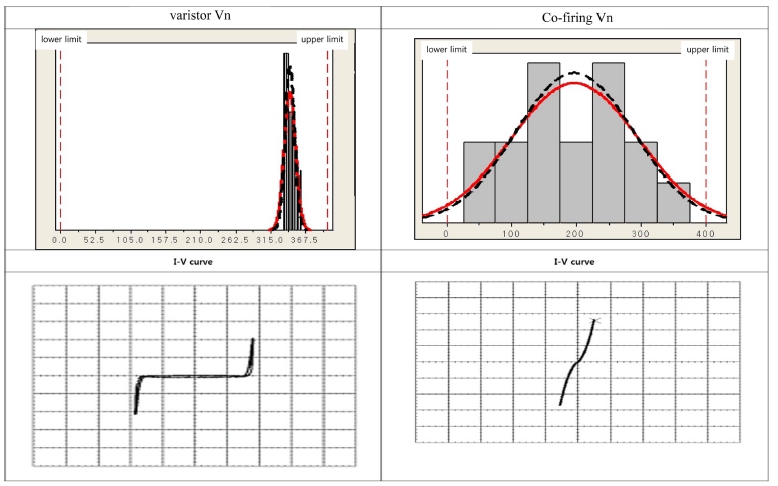

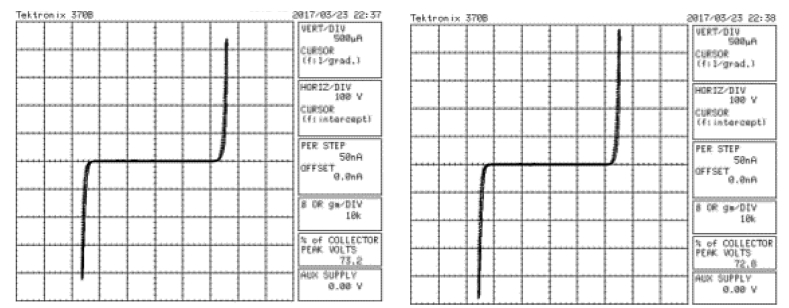

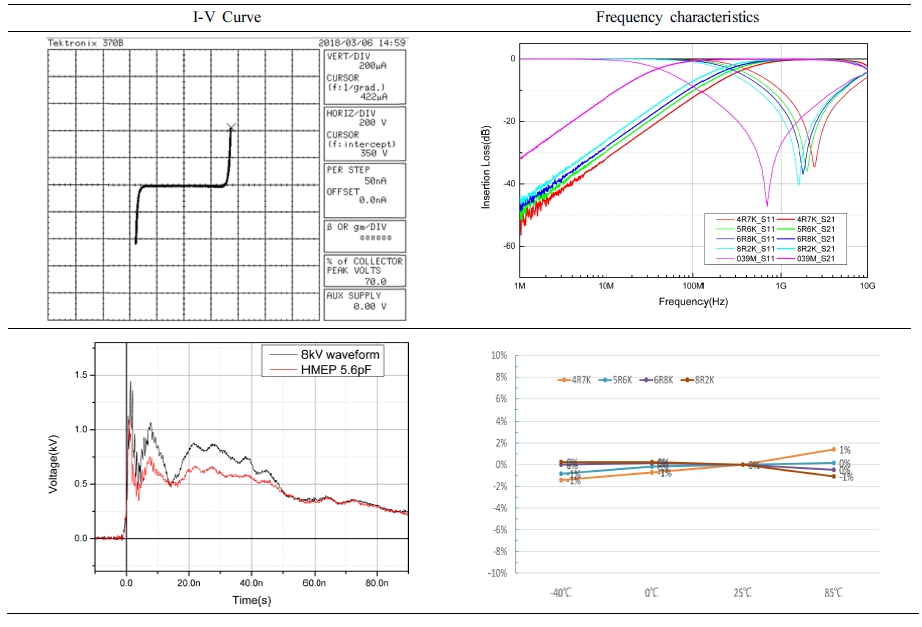

앞에서 기술한 것 처럼 바리스터와 캐패시터를 원칩화 하기 위해 두께를 얇게 따로 만들어 접착제로 붙인 후 Ag 에폭시를 이용하여 외부전극을 형성하고 Ni/Sn 도금 하여 제작한 칩과 기존 바리스터 제품과의 비교 결과는 Fig. 3과 같다. 바리스터의 특성을 나타내는 I-V curve 와 ESD 파형의 그래프를 나타내었는데, 접합한 바리스 터와 기존 바리스터가 서로 유사한 특성 결과를 나타내 었다. 이는 사이즈의 축소에도 불구하고 기존 바리스터 제품과 유사한 특성을 나타냄을 알 수 있다.

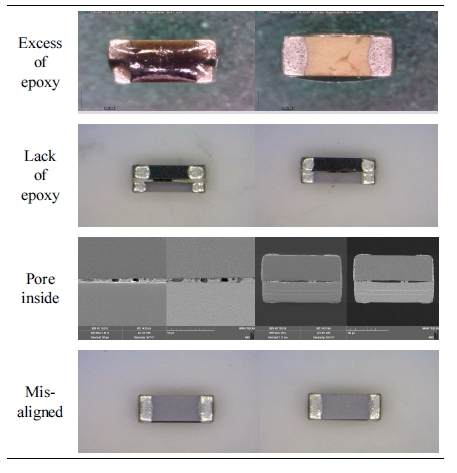

인쇄를 통한 접합부 형성 시 발생되는 불량을 Table 3에 나열하였으며, 이는 스크린의 도포 면적, 메쉬 사양, 유제 두께 및 설비 세팅 조건 등을 변경하여 많은 부 분 해결하였으나 완벽한 일체화는 한계가 있다.

3.2 동시 소성형 개발

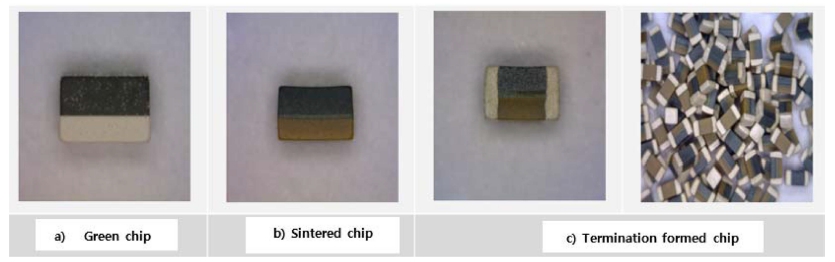

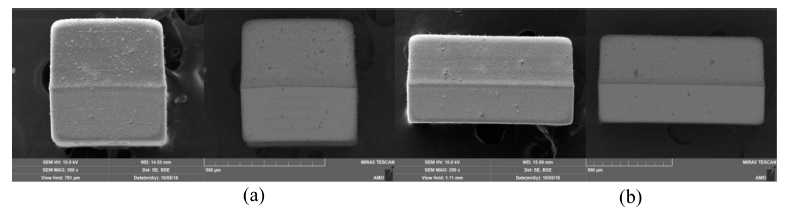

적층형 바리스터와 적층형 캐패시터를 일체화하기 위 해 미리 시트를 준비하고 각 특성에 맞게 인쇄한 후 수 동 적층기를 이용하여 적층 후, 라미네이션 공정을 통 해 일체화된 그린 칩을 제작하였다. 이후 소성 후 에폭 시 외부전극을 입히고 경화하였다. 각 공정 진행에 따 른 시료의 이미지는 Fig. 4와 같다.

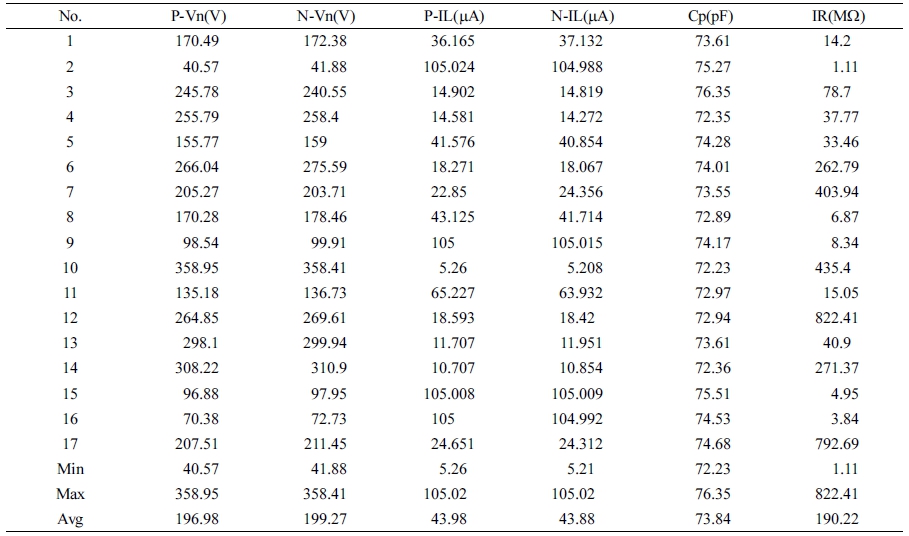

전기적 특성 측정 결과 커패시턴스의 경우 73pF 구현 하였으며, Table 4와 같이 ±5 %의 이내의 산포를 갖는 우수한 특성산포 값을 얻을 수 있었다.

바리스터 특성의 경우 전극간 거리, 소결온도에 따른 ZnO의 입자 크기에 따라 특성이 결정된다. 설계에 따른 목표 바리스터 특성을 min=340 V 기준으로 설계하였다. 일반 바리스터 단품의 경우 Fig. 5와 같이 좁은 바리스 터 특성산포와 정상적인 I-V Curve가 구현된 반면, 바 리스터와 커패시터를 동시 소성한 시료에서 300 V 이하 의 넓은 바리스터 특성산포와 바리스터 특성의 열화 또 는 Short 수준의 I-V Curve가 확인되었다.

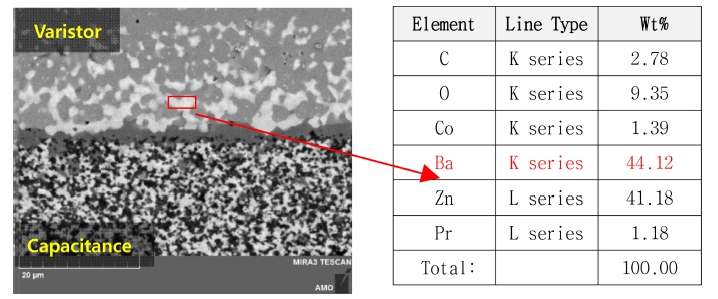

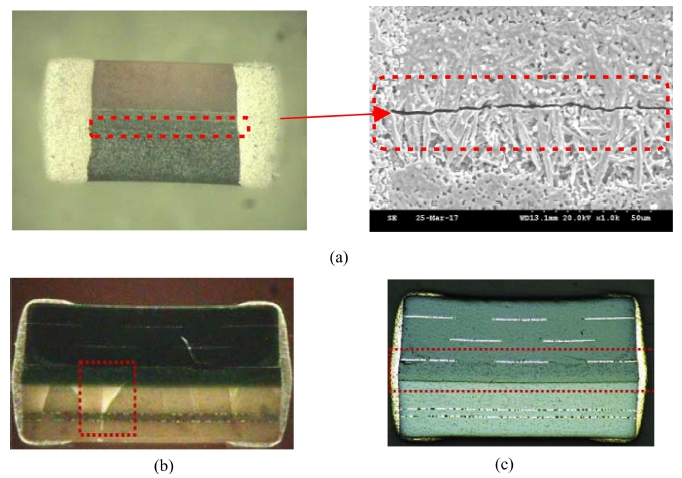

제작된 시료의 외관 및 내부의 미세구조를 Fig. 6과 같 이 관찰하였다. 외관을 분석한 결과 이종접합 면에서 크 랙이 발생되었으며 접합면 바리스터 쪽에서 2차상이 관 찰되었다. 또한 내부 분석결과 이종접합 면과 인접한 바 리스터에서 길이 방향, 캐패시터에서 두께 방향으로 각 각 크랙이 발생되었다.

Fig. 6

Observation of micro microstructure: (a) appearance, (b) cross sectional view of capacitor, (c) varistor.

이종접합 면에서 바리스터 쪽으로 2차 상으로 보이는 미세조직이 관찰됨을 통해 소결공정 진행 시 캐패시터의 성분이 바리스터 쪽으로 확산되어 영향을 미쳤을 것으로 예상된다. 이는 이종접합 면의 바리스터 조직의 성분분 석 시 Ba 성분이 검출된 Fig. 7과 일치하는 결과이다.

세라믹 조성인 BaTiO3에서 소성 시 Ba 성분 확산이 진행되어 2차 상이 발생되고, 이로 인해 바리스터/ Ba 성분이 확산된 바리스터/ 커패시터 층 사이의 수축율 차 이로 크랙이 발생되고 바리스터 특성이 short 수준으로 낮게 나타남을 예측할 수 있었다.

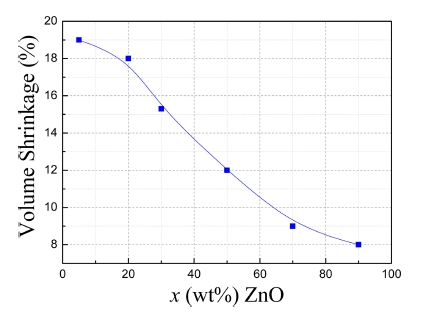

3.2.2 버퍼층 개발

소성 시 세라믹의 성분이 바리스터 쪽으로 확산되어 바 리스터 특성이 열화 또는 short 현상과 크랙을 방지하기 위해 이종접합 되는 면 사이에 들어갈 버퍼 층을 개발 하였다. 버퍼층의 주요 역할은 동시소성 시 세라믹의 성 분이 바리스터로 확산되는 것을 방지하여 바리스터 특성 을 구현되게 하며, 2차상 발생을 억제하여 수축율 차이 에 의한 크랙 방지에 그 목적이 있다. 버퍼층의 주 성분 은 반응성이 낮은 ZrO2을 주성분으로 하고, 소성 후의 수 축율을 세라믹과 바리스터에 맞추기 위하여 ZnO를 치환 하며 수축율을 평가하였다. Fig. 8은 1,100 °C에서 4시간 동안 소결한 (Zr1-x)(Znx)O3(x=5, 20, 30, 50, 90) 조성을 가지는 버퍼층의 직경 수축율 결과이다. ZnO의 치환량이 증가 할수록 수축율의 증가 속도는 감소하였다. 바리스터 와 최종 수축율을 일치시키기 위해 ZnO의 치환량은 10 wt%로 결정하였다. 바리스터와 버퍼층의 수축율을 일치 시키고 동시소성 시 크렉 발생 여부와 바리스터 특성이 구현되는지 확인하였다. Fig. 9은 바리스터와 버퍼층을 그 린 시트 상태로 부착하여 동시 소성된 시료이며, 각각의 수축율이 유사한 수축된 정도를 보이며 크랙은 발생되지 않았다. 또한 바리스터 특성은 Fig. 10과 같이 I-V Curve 를 통해 정상적으로 나타남을 확인하여 (Zr9Zn1)O3조성 을 버퍼층으로 적용 가능할 것으로 판단된다.

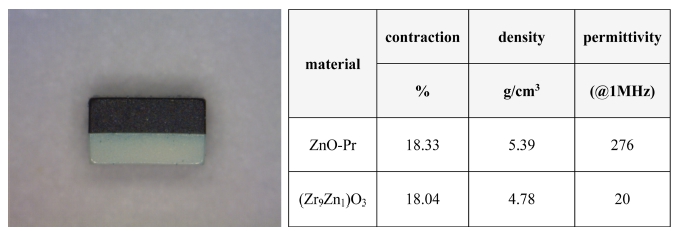

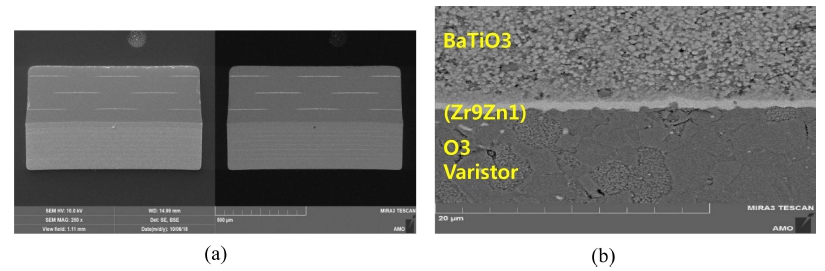

3.2.3 버퍼층을 통한 바리스터와 세라믹 동시소성

Fig. 3의 모식도와 같이 바리스터와 세라믹 접합면 사 이에 버퍼층을 넣어 동시 소성 시료를 제작하였다. 버 퍼층의 두께는 35 um로 하였고, 세라믹조성의 경우 Fig. 9와 같이 수축율이 유사한 조성을 적용하였다. 소성은 1,100 °C에서 4시간 동안 진행하였으며, 소성 완료된 시 료들에 대해 외관 분석과 내부 단면 분석을 진행하였 다. 버퍼층을 삽입함에 따라 Fig. 11, Fig. 12와 같이 이 종접합 면에서 나타났던 크랙이 개선됨을 확인할 수 있 다. 이는 버퍼층 삽입에 따라 캐패시터부의 Ba 성분이 바리스터 쪽으로 확산되는 것을 방지한 효과이며, Fig. 12(b)와 같이 버퍼층과 인접한 바리스터의 미세조직이 균 일하게 관찰됨으로 이를 확인할 수 있다.

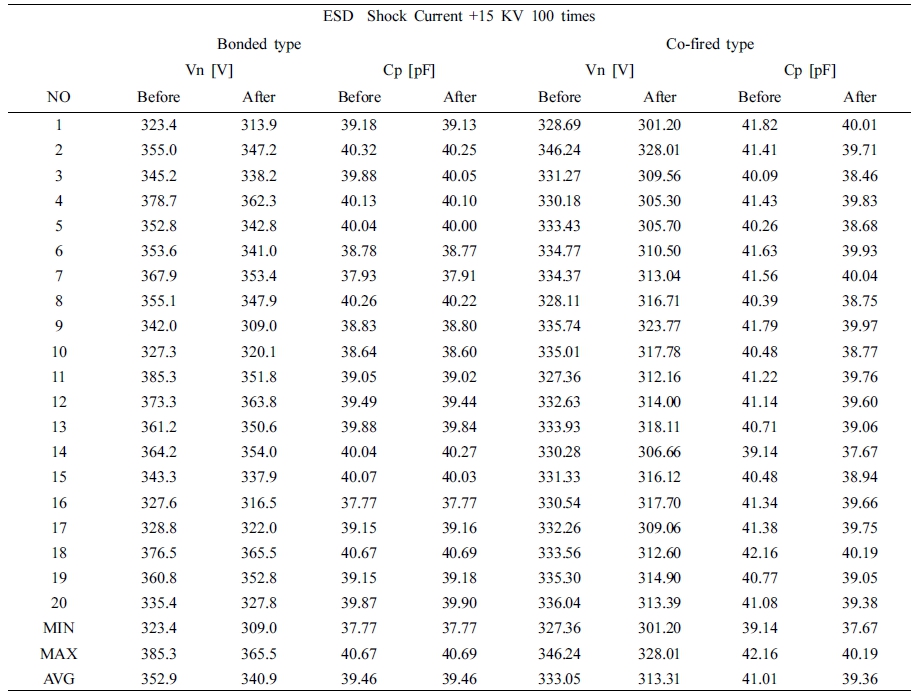

3.2.4 접착제를 이용한 칩과 특성 비교

에폭시를 이용해 접합한 시료와 동시소성 시료의 특성 비교를 위해 외부전극 형성 후 Ni-Sn 도금 처리를 하 였다. 전기적 특성은 SMD 후 캐패시턴스, 바리스터 특 성을 측정하였고 ESD 15 kV 100회 인가 후 특성을 재 측정하여 ESD 내성을 확인하였다. 접합형과 동시소성형 의 특성 비교 결과 유사한 바리스터, 캐패시턴스 특성 을 확인할 수 있었고, ESD 내성 또한 유사함을 Table 5를 통해 확인하였다.

또한 테스트 결과를 통하여 다음과 같이 2개소자의 기 능을 만족하고 있음을 확인하였다. Table 6에서 보는 것 과 같이 I-V curve는 기존의 바리스터와 거의 유사한 성 능을 가지며, ESD특성 또한 8 kV open waveform과 유 사한 ESD 파형 결과를 얻었다. 주파수 특성은 감전소 자와 거의 동일한 S-parameter의 결과 및 온도 특성을 보이므로 감전소자와 바리스터의 성능을 동시에 만족하 는 제품이라고 할 수 있다.

4. 결 론

첫번째로 바리스터와 감전소자를 접합한 제품이 출시 되었고, 기존 제품과 사이즈측면에서 동일하며, 두 소자 의 특성을 동시에 구현한 동시소성 제품을 출시하였다. 해당 제품의 특성을 요약하면 다음과 같다.

접합품 대비 안정적인 구조 및 고 신뢰성을 보이며 양 산에 유리하다.

버퍼층은 이종 칩과 수축율을 맞춰 크랙을 억제하며 이 종 성분의 확산을 억제하여 캐패시터 및 바리스터 특성 을 만족한다.

동시소성 칩은 단말기에서 요구되는 ESD 8kV 특성을 만족하였다.

캐패시터는 RF에서 사용되는 캐패시터와 동일한 특성 을 보이고 있으며 RF 회로에 필요한 안정적인 온도 변 화율을 보이고 있다.

주파수 특성은 감전소자와 거의 동일한 S-parameter의 결과를 보이므로 감전소자와 바리스터의 성능을 동시에 만족하는 제품이라고 할 수 있다.