1. 서 론

2. 인공지능 반도체

2.1. 신경처리장치(neural processing unit, NPU)

2.2. 엣지 컴퓨팅(edge computing)

2.3. 뉴로모픽 반도체

3. 유리 코어 기판과 인터포저

3.1. 유리 소재의 특성과 인터포저의 적합성

4. AI 반도체 패키징

4.1. 칩렛(chiplet)

4.2. TGV 기술과 솔더링

4.3. 유리 기판 상 금속 코팅 및 TGV 범핑 적용

5. 결 론

1. 서 론

Artificial intelligence (AI) 반도체는 인공지능 알고리즘을 사용하여 여러 응용 프로그램을 실행하는 데 최적화된 반도체이다. 이러한 반도체는 대량의 데이터 처리 및 복잡한 계산을 수행하는 데 효율적이며, 빠른 속도와 낮은 전력 소비와 같은 장점을 가지고 있어 지능형 반도체라고 불린다. AI 반도체는 보통 인공 신경망과 같은 AI 모델의 학습 및 추론의 가속화가 필요한 데이터 센터, 클라우드, 자율주행 자동차, 모바일 기기 등 다양한 분야에서 활용되고 있다.

최근 모바일 및 통신 시스템 분야에서의 고속 데이터 전송 및 방대한 데이터 처리에 대한 요구가 증가함에 따라 글로벌 기업마다 독자적인 성능의 AI 반도체 개발에 집중하고 있다. 해외시장조사업체 Statista에 따르면 글로벌 인공지능 시장의 가치는 2024년에 254조 원을 넘어섰으며, 2030년에는 약 1,140조 원까지 상승할 것으로 예측하였다.1) 금후 인공지능 반도체의 수요가 증가함에 따라 다수의 프로세서 칩을 상호 연결할 수 있는 고밀도 패키징 기술이 요구된다. 그러나 기존의 유기(organic) 기판은 열팽창계수(coefficient of thermal expansion, CTE) 불일치 등의 문제로 인해 고밀도 패키징의 요구를 충족시키는데 한계가 있다.2)

현재 유기 기판과 인터포저로는 제한된 공간 안에 여러 칩들을 고밀도로 집적하는 데 한계를 맞이하면서 유리를 사용한 기판과 인터포저가 주목받고 있다. 유리 소재는 보통의 유기 소재보다 강도가 높고, 보다 나은 절연 성능과 열적 안정성, 균일한 표면 등의 이점이 있다.3) 본 고에서는 최근 주목받고 있는 AI 반도체 및 유리를 사용한 기판, 인터포저와 이와 관련된 패키징 기술인 through glass via (TGV) 관련 연구에 대해 조사하였다. 아울러, 저자들이 연구한 TGV 범핑 기초 실험 결과를 소개하였다.

2. 인공지능 반도체

2.1. 신경처리장치(neural processing unit, NPU)

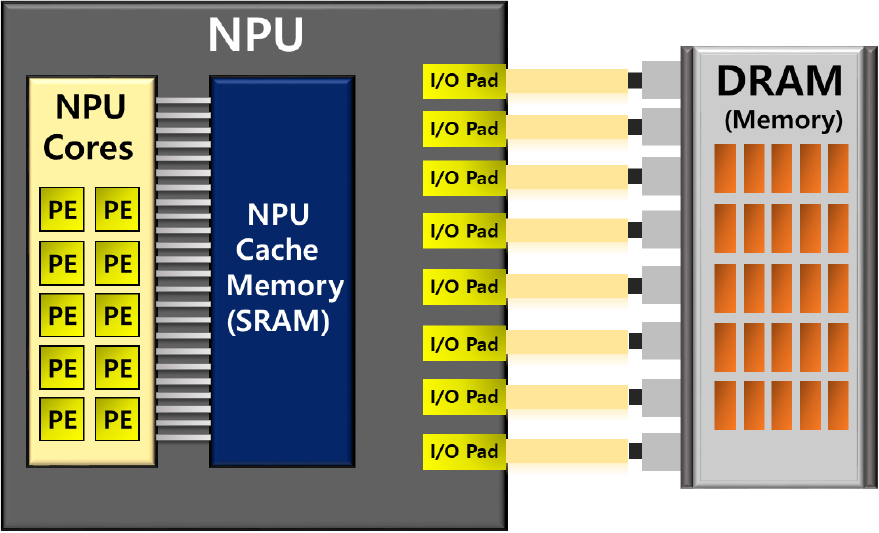

NPU는 모바일, 자율 주행 자동차, 클라우드 서버와 같은 고성능 컴퓨팅이 필요한 분야에서 활용되며, 중앙처리장치(central processing unit, CPU), 그래픽처리장치(graphics processing unit, GPU)와 다르게 딥러닝(deep learning)과 머신러닝(machine learning)을 기초로 한 인공지능에 최적화된 하드웨어이다. 일반적으로 NPU는 다수의 processing engine (PE)로 구성되며, 인간의 뉴런처럼 서로 연동하며 대규모의 데이터를 동시에 처리한다.4)Fig. 1은 인공지능 학습을 위한 NPU 패키징 구조 모식도로, NPU에는 본질적으로 데이터 저장의 역할을 할 수 있는 외부 메모리(dynamic random access memory, DRAM)가 필요하다. 그 이유는 최근에 생성되는 대형 인공지능 학습 모델은 변수마다 100 MB 이상의 크기로 구성돼 있어 방대한 양의 데이터를 처리하기 어렵기 때문이다.5)

CPU대신 NPU를 사용하는 경우 20배정도 더 빠른 연산이 가능하지만 CPU는 32비트를 사용하는 반면 NPU는 8비트 또는 16비트를 사용하므로 정확도 측면에서 단점을 보인다.6) 그러나 NPU의 8비트 연산 방식때문에 인공지능의 데이터 처리시간을 약 50~65 % 단축시켜 전력 소모 측면에서 10배에서 20배정도 더 효율적이다.7) 따라서 차세대 AI반도체를 위해서는 CPU, GPU, NPU를 조합한 최적의 패키징 방식을 찾는 것이 중요하다. 최근에는 CPU와 NPU를 결합하여 메모리를 같이 공유하도록 패키징하는 방법이 연구되었으며,8) Yazdanbakhsh 등9)은 NPU와 GPU를 함께 패키징한 NGPU에 대해 보고하였다. NGPU는 기존 GPU 아키텍처에 비해 2.4배 평균속도 향상과 2.8배 평균전력 소모량 감소를 보여주었다.

2.2. 엣지 컴퓨팅(edge computing)

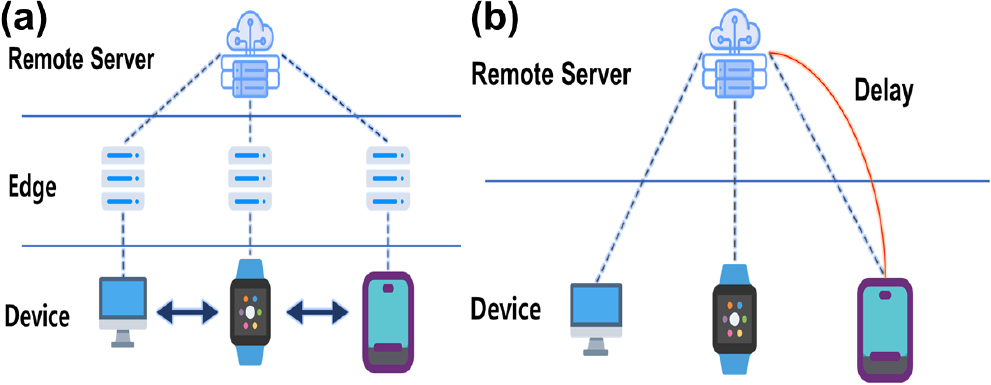

엣지 컴퓨팅 반도체는 데이터 센터와 같은 중앙 제어식 위치가 아닌 사용자의 디바이스에서 AI를 사용하는 반도체를 의미한다.10)Fig. 2는 원격 서버에서 데이터를 처리하는 방식을 비교한 예를 나타낸 그림이다.

기존 체계는 컴퓨팅 장치가 멀리 떨어진 데이터 센터에 위치하여 신호 지연, 대역폭 감소, 정보 보안 등의 문제가 발생할 수 있다. 반면에 엣지 컴퓨팅을 이용한 AI반도체는 서버와 기기 간에 신호 지연을 줄여 디바이스에서 실시간으로 인공지능 이용이 가능해진다.11) 이는 스마트시티, 웨어러블 디바이스 등의 여러 분야에 적용될 수 있을 것으로 기대된다.12)

2.3. 뉴로모픽 반도체

뉴로모픽 반도체란 신경망의 계층적 구조와 병렬 처리를 모방하여 설계된 집적 회로로, 기존의 반도체 처리 체계와는 다른 접근 방식을 채택하고 있다.13) 인간의 뇌에서는 뉴런과 시냅스에 의해 신호가 전달되지만 현대의 전자 기기는 메모리와 컴퓨팅 프로세서가 물리적으로 분리되어 정보를 처리한다. 여기서 메모리와 프로세서 간 데이터 이동에 의해 컴퓨팅이 느려지고 많은 전력이 소비되는 ‘폰 노이만 병목 현상(Von Neumann bottleneck)’이 발생할 수 있다.14) 이러한 폰 노이만 병목 현상을 해결하기 위해 프로세서와 메모리 간의 밀접한 통신을 할 수 있게 하는 high bandwidth memory (HBM)가 고안됐다. HBM은 through silicon via (TSV)를 이용하여 DRAM을 3차원으로 적층함으로써 신호 전달 경로를 단축한 기술이다.15) 그러나 이러한 접근 방식에서도 메모리와 프로세서의 물리적 분리는 여전히 존재하게 돼 병목현상이 발생할 수 있다.16) 이러한 문제를 해결하기 위해 메모리 자체적으로 계산을 수행할 수 있는 ‘인-메모리(in-memory)’기술을 위해 뉴로모픽 반도체를 개발할 필요가 있다.17)

3. 유리 코어 기판과 인터포저

3.1. 유리 소재의 특성과 인터포저의 적합성

전자기기 산업의 여러 기업들은 실리콘 웨이퍼에 포토, 식각, 증착 등의 복잡한 공정을 거쳐 소자를 생산한다. 소자들은 각각 다른 크기의 패드와 피치를 가지는데, 최종 어셈블리 과정에서 이들을 연결하기 위해 기판을 따로 제작하는 과정은 상당한 공정 비용을 수반한다. 이러한 문제를 해결하기 위해 인터포저 기술이 등장하였다. 인터포저는 칩과 기판 사이에 위치한 배선층으로써 미세 집적회로를 삽입하였기 때문에 여러 칩들을 전기적으로 연결하고, 배선 범위를 확장하는 것이 가능하다. 이렇게 다수의 input/output (I/O)를 구현한 인터포저는 미세 금속 배선과 TSV 등을 통해 메모리 칩이나 로직 다이(logic die) 등을 연결할 수 있으며, 이를 2.5D 패키징이라고 한다.

대개 인터포저는 유기 인터포저와 실리콘 인터포저가 존재한다. 유기 인터포저는 폴리아미드(polyamides)나 불소중합체(fluoropolymer)와 같은 유기 재료로 제작되며, 실리콘보다 저렴하기 때문에 비용적인 측면에 이점이 있다.18) 그러나 보통의 유기 소재는 실리콘이나 유리 소재 대비 상대적으로 높은 열팽창계수(50 ppm/°C)로 인해 칩과 기판의 접합부가 휘는 휨 현상(warpage)이 발생할 가능성이 있다.19) 휨 현상은 칩, 인터포저 등 반도체 부품의 평면도에 변형이 발생 하는 것으로, 소재 간의 열팽창계수 차이나 공정 중의 온도 변화, 불균일한 응력 분포 등이 원인일 수 있다. 휨 현상은 기판-인터포저-칩 사이의 접합 불량을 야기하므로 공정 중 필수적으로 고려해야하는 사항이다. 최근에는 폴리아미드 군에 속하는 액정폴리머(liquid crystal polymer)를 사용하는 연구도 진행되었으며, 액정폴리머의 열팽창계수는 16~17 ppm/°C정도로 Cu의 열팽창계수와 비슷하기 때문에 변형이 적다는 장점이 있어 주목을 받고 있다.20) 해당 연구는 기존 실리콘 인터포저와 유기, 액정폴리머 인터포저 기술 간의 시스템과 성능 및 신뢰성 수준을 비교 연구를 수행했다는 점에서 고밀도 패키징 분야의 도약을 이뤘다는데 의의가 있다. 추가적으로 반도체 산업에서 사용되는 유기 인터포저의 대표적인 예로는 re-distribution layer (RDL) 인터포저가 있다.

실리콘 인터포저는 실리콘 웨이퍼 기반으로 하는 고밀도 신호 연결 및 배선 재분배층으로, 그 예로는 embedded multi-die interconnect bridge (EMIB)가 있다. 실리콘의 열팽창계수는 3.1 ppm/°C정도이기 때문에 공정 시 휨 현상 발생을 제어하기 위해서는 이와 비슷한 열팽창계수를 가진 배선 금속 소재를 선택해야 한다. 그러나 보통 배선 금속으로 Cu가 사용되며, Cu의 열팽창계수는 17 ppm/°C정도이다. 실리콘은 유기 소재보다 상대적으로 Cu와 열팽창계수 차이가 적지만 약 14 ppm/°C 정도의 차이가 존재하기 때문에 휨 현상 발생에 대한 위험이 존재한다.21) 이 연구는 TSV 면적 비율, TSV 높이(웨이퍼 두께), 온도에 의해 영향을 받는 열팽창계수를 수치화하여 대규모 3D 패키지 모델링을 위한 신뢰할 수 있는 정보로 사용할 수 있게 하였다. 최근 휨 현상 원인에 대한 대처로써 유리 인터포저에 대해 많은 연구가 진행되고 있다. 제조하는 유리의 성분에 따라 상대적으로 실리콘보다 배선 금속과의 열팽창계수 차이를 조절할 수 있기에 전자기기 산업계의 주목을 받고 있다.

신뢰성 높은 TGV를 얻기 위해서는 소재의 영률(young’s modulus)도 고려할 필요가 있다. 영률은 소재의 탄성 계수를 나타내며, 소재가 외부 힘을 받았을 때 변형되는 정도를 나타내는 지표이다. 높은 영률을 가진 소재는 높은 강성(rigidity)과 탄성 변형에 대한 높은 저항성을 나타내지만 탄성 한계를 초과하는 힘이 가해질 경우 쉽게 부러지거나 깨질 수 있다. 이를 토대로 Jeong 등22)은 기존의 TSV 계면의 열적 특성을 분석하기 위한 연구를 진행하였다. 식 (1), 식 (2)는 TSV 비아에서 발생되는 Cu와 실리콘의 열팽창계수 차이로 인한 계면 분리를 수식화한 것이다. 여기서, G는 에너지 해방률, E는 영률, ∆α는 CTE 불일치(mismatch), ∆T는 열 부하(thermal load), D는 TSV 직경, ν는 포아송비(Poisson’s ratio)를 나타낸다.

위 식을 통해 Jeong 등22)은 같은 열 부하 조건에서 냉각 구간이 가열 구간 대비 에너지 해방률이 약 35 %정도 높음을 알 수 있었다. 이는 냉각 시, 가까운 실리콘 벽면에서 균열의 연쇄 반응으로 인해 시드층(Cu)이 보다 쉽게 탈락됨을 의미하였다. 이를 토대로 유리의 계면에 적용시켜 볼 수 있었다. 이전에 연구된 유리의 영률은 약 62.8~74 GPa정도이며, 실리콘의 영률은 165 GPa정도이다.23) 즉, 동일 조건에서 유리는 실리콘보다 상대적으로 CTE 불일치와 영률이 낮으므로 에너지 해방률이 작아져 보다 나은 계면 특성을 가질 것으로 예상할 수 있다.

Table 1은 인터포저에서 사용되는 여러 소재들의 열적, 기계적 특성을 분석한 내용이다. 열전도도(thermal conductivity)는 물질이 열을 전달하는 능력을 의미하며, 단위 시간당 이동하는 열과 온도 구배의 면적과의 관계로 정의할 수 있다. 열확산도(thermal diffusivity)는 재료가 열을 전달하는 속도를 나타내는 물리적 성질로, 열전도도, 밀도, 비열과의 관계식이다. 실리콘의 경우 열이 가해졌을 때 열 전달이 빠르지만 상대적으로 유리는 그 정도가 낮다.24,25,26,27,28,29,30,31) 다시 말해 동일 면적을 접합 했을 때 유리는 실리콘보다 열전도가 상대적으로 느려서 열이 가해지는 접합 부근의 온도 상승을 제어한다면 칩 전체에 가해지는 손상을 줄일 수 있다.

Table 1.

Thermo-mechanical properties of glass, Si, Cu and organic materials.

기판이나 인터포저로 사용할 수 있는 유리는 석영 유리(fused silica), 붕규산 유리(borosilicate glass), 라임 소다 유리(lime-soda glass), 규산알루미늄 유리(alumino silicate glass), 무알칼리 유리(alkali-free glass) 등이 있다.32) 석영 유리는 SiO2가 결정 상태를 이루고 있는 유리로써 1,000 °C 이상의 고온에서도 사용 가능하다.33) 또한 석영 유리는 광학적, 화학적, 열적 특성이 우수하여 반도체, 디스플레이 등의 재료로 사용되기도 한다.34,35,36,37) 붕규산 유리는 SiO2 (80 %), B2O3 (15 %), Na2O & K2O (5 % 이내)로 구성된 유리를 말하며, 융점은 1,600 °C정도이다.38) 실리콘이 최대 융점이 1,350 °C정도인 점과 비교하면 유리 소재들은 실리콘보다 내열성이 우수하지만 유리전이온도가 존재하여, 이 온도 이상에서는 물성이 변할 수 있기 때문에 이를 고려해야 한다. 또한 상온에서 유리는 절연체의 성질을 가지지만 고온 및 나트륨이 많이 함유되어 있는 유리일수록 나트륨 이온이 매개체가 되어 전하가 잘 이동할 수 있게 되어 전도성이 향상된다.39) 이는 온도가 상승할수록 전기저항이 감소한다는 것을 의미하며, 이로 인해 관통홀이나 배선을 통과할 전류가 기판에 흐르게 될 수 있기 때문에 적합하지 않을 수 있다.

4. AI 반도체 패키징

4.1. 칩렛(chiplet)

System on chip (SoC)는 하나의 칩 안에 CPU, 메모리, 입출력 장치 등의 구성 요소들이 통합된 반도체 형태이다. SoC는 여러 시스템을 하나의 칩으로 구현함으로써 공정 단순화, 적은 소비전력 등의 장점을 가져 초기 스마트폰, 태블릿 등 모바일 기기에 적용하였다. 그러나 현재는 CPU와 메모리 이외에도 로직, 통신 소자, 이미지 센서 등 여러 소자와 기기의 소형화로 공간적 제약이 발생하였고, 이를 한 칩에 모두 집적하는 데에 어려움이 발생하였다.

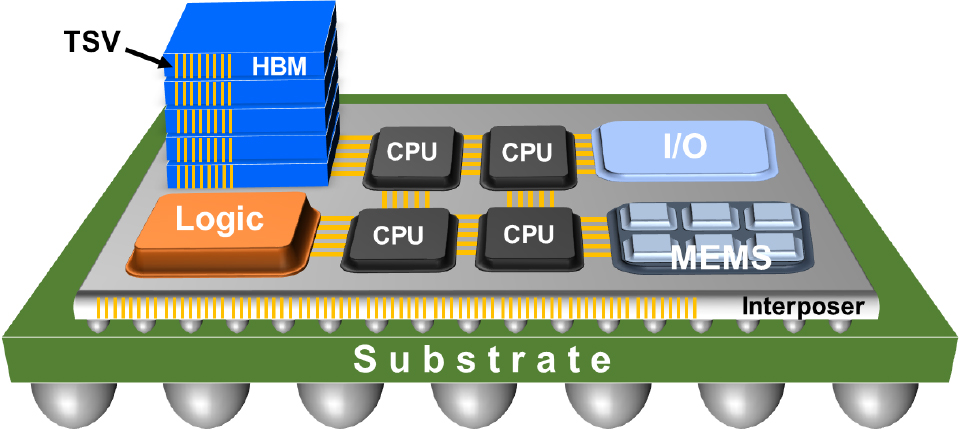

Fig. 3은 SoC 패키징의 부족한 점을 보완하기 위해 제시된 칩렛(chiplet) 기술을 나타낸 그림이다. chiplet은 각각 다른 기능을 하는 칩들을 단일 칩에 통합하는 기술로써 기존 모노리틱(monolithic) 패키징보다 향상된 효율성과 수율, 최신 기술 적용 및 공정 시간 단축에 용이하다.46) 보통 칩의 크기가 클수록 반도체 제조 수율은 감소하며, 모노리틱 다이는 15 %정도의 수율을 얻을 수 있지만 이를 4개의 칩렛 구조로 바꾸면 수율이 37 %정도 상승할 수 있다는 보고가 있다.47)

그 예로, I사는 2019년에 3D 칩렛 구성 방식인 omni-directional interconnect (ODI)를 제시하였고, 이는 칩렛과 칩렛을 수평, 수직으로 연결하는 기술이며, 약 70 µm정도의 TSV 인터포저를 통해 연결하였다고 보고한 적있다. 2020년에는 ODI가 적용된 레이크필드(Lakefield) 프로세스를 출시하여 제품화 한 적 있다. 레이크필드는 중심 CPU와 주변의 작은 CPU들이 칩렛 형태으로 배치되며, chip on wafer (CoW) 기술과 Cu-pillar 위에 Sn-Ag 범핑이 적용된 사례이다.48,49)

2023년 A사50)는 5 nm 공정을 통해 생산된 칩 12개를 연결한 chiplet 패키징 기술을 제시하였으며, 이는 칩렛 당 최대 896 GB/s의 데이터를 전송할 수 있다고 발표하였다. 이는 기존 인공지능 연산 능력보다 1.6배 높은 성능 수준이며, 생성형 AI에 적합하다고 평가받고 있다.

이러한 산업계의 노력에도 금후 제타바이트(zettabyte)를 넘어선 방대한 데이터를 생성 및 연산하는 인공지능 반도체를 위해서는 기존 소재와 패키징 기술보다 고밀도, 고집적이 가능한 유리 기판과 이와 관련된 차세대 패키징 기술이 필요한 시점이다.

4.2. TGV 기술과 솔더링

TGV 기술이란 기존 TSV의 단점를 보완할 수 있는 패키징 기술로써 유리 기판에 관통홀(via)을 형성하여 전기적 신호를 수직으로 빠르게 전달하는 기술이다. 다량의 데이터를 전송, 처리하는 AI 반도체를 만들기 위해서는 현재 반도체의 경박단소화로 인해 발생된 공간적 제약을 극복하고, 고밀도 연결을 할 수 있는 기술이 필요하다. 우선 유리에 관통홀을 형성하기 위한 방법은 레이저를 활용한 laser induced selective etching (LISE) 기술과 전기 방전을 이용한 electrical discharging method (EDM) 등의 기술이 있다.51,52) 형성된 유리 관통홀에 Cu를 충전하기 위해서는 관통홀 측벽에 기능성 박막을 형성하는 과정이 필요하다. 그러나, 유리는 이온 및 공유 결합으로 이루어진 비정질의 결정 구조를 가지고, 금속은 금속 결합을 통해 일정한 구조를 유지하려는 상반된 성질 속에서 균일하고, 박리가 발생하지 않는 기능성 박막을 형성하는 데에는 여러 어려움이 있다.53)

일반적으로 박막을 형성하는 방법에는 건식코팅법, 습식코팅법이 존재하며, 건식코팅법에는 스퍼터링, 습식코팅법에는 전기도금이나 무전해도금이 있다.54) 반도체에 사용될 유리의 소재에 따른 적절한 박막 형성 공정을 선택하여야 하며, 관통홀 측벽의 시드층(seed layer) 코팅이 제대로 수행되지 않으면 공정 중 박막이 박리될 우려가 있다.

한편, 유리 기판 위에 범핑 및 솔더링을 하기 위해서도 아래와 같은 적절한 공정이 필요하기도 하다. 일반적으로 솔더링 신뢰성을 향상시키는 방법으로는 솔더의 젖음성(wettability)과 부착성(adhesion)을 향상시킬 수 있도록 Zr, Ce, Ti와 같은 활성 금속 원소를 첨가한 솔더를 사용하거나, 금속화(metallization)층을 사용한 솔더링 프로세스를 통해 접합부에 intermetallic compound (IMC)를 형성시켜 접합 특성을 향상시키는 방법이 있다.55)

Yonekura 등56)은 초음파 보조 솔더링(ultrasonic assisted soldering)을 통해 유리 기판에 무연 솔더를 접합하는 메커니즘을 연구하고, 초음파 처리가 솔더링 특성에 미치는 영향을 조사하였다. 이 연구에서는 Sn-Zn-Sb 솔더와 초음파 보조 솔더링 장치를 사용하여, 5 W의 전력과 60 kHz의 주파수의 초음파 처리가 수행되었다. 솔더링 공정은 623 K에서 약 2초간 진행되었으며, 이후 실온에서 냉각되었다. 실험 결과, 초음파 처리를 적용하였을 때 전단강도는 평균 2.90 MPa로 나타났다. SEM 이미지에서는 접합부의 IMC 층이 발견되지 않았지만 TEM 분석 결과, 접합 계면 부근에서 0.5 nm정도의 얇은 층이 발견되었다. 한편 솔더링 과정에서 초음파 처리를 적용하지 않았을 때에는 낮은 젖음성 특성으로 인해 솔더가 유리 표면에 접합되지 못함을 확인하였다.

Li 등57)은 SiO2 유리와 Sn-based 솔더를 접합하고, SiO2/Sn/Al 접합부의 기계적 특성에 대한 연구를 진행하였다. 이 실험에서는 99.0 wt% SiO2의 유리 기판과 230 °C의 낮은 융점을 가진 Sn 솔더가 사용되었다. 솔더링 시 초음파를 가해 유리 위 솔더의 젖음성을 향상시켜 접합을 진행하였고, SiO2 접합부의 전단강도는 16 MPa이었다. 또한, Li 등은 접합부의 기계적 특성 향상을 위해 Sn 솔더 사이에 두께 0.1 mm의 Cu interlayer을 삽입하여 전단강도의 변화를 관찰하였다. 실험 결과, SiO2/Sn/Cu/Sn/Al 접합부의 파단(fracture)은 Cu6Sn5, Cu3Sn IMC에 의한 취성(brittle) 파괴를 보였으며, 접합부의 전단강도는 28 MPa이었다. 파단이 유리 기판과 솔더의 접합부가 아닌 IMC를 통해 발생한 점으로 보아 유리와 금속의 접합에 대한 긍정적인 사례를 제시하였다.

Töpper 등58)은 유리 인터포저 상에 형성된 범프의 기계적 특성을 조사하였다. 이 실험에 사용된 유리 웨이퍼의 두께는 500 µm이며, 10 µm 이하의 total thickness variation (TTV)을 가진다. 범프의 접합성을 향상시키는 복합금속층인 under bump metallization (UBM)은 TiW/Cu (sputtering), Ni (electroplating)이 웨이퍼 상에 코팅되었다. 이후 Töpper 등58)은 고속 레이저 천공법(laser drilling)으로 관통홀을 형성하였으며, 약 100 µm 피치의 직경 250 µm인 TGV를 제작할 수 있었다. 솔더볼 리플로우를 통해 형성된 범프의 전단강도는 약 2.45~3.43 N이며, 열적시효시험(thermal cycling test, range : -55~125 °C, 250 cycles) 후의 전단강도는 약 2.1 N이었다. 이 연구는 TSV와 TGV의 비교를 통해 추후 전자 기기 패키징 방안을 모색하고 있으며, 유리 인터포저 상의 솔더 범프의 열적, 기계적 신뢰성에 대해 고찰하였다.

4.3. 유리 기판 상 금속 코팅 및 TGV 범핑 적용

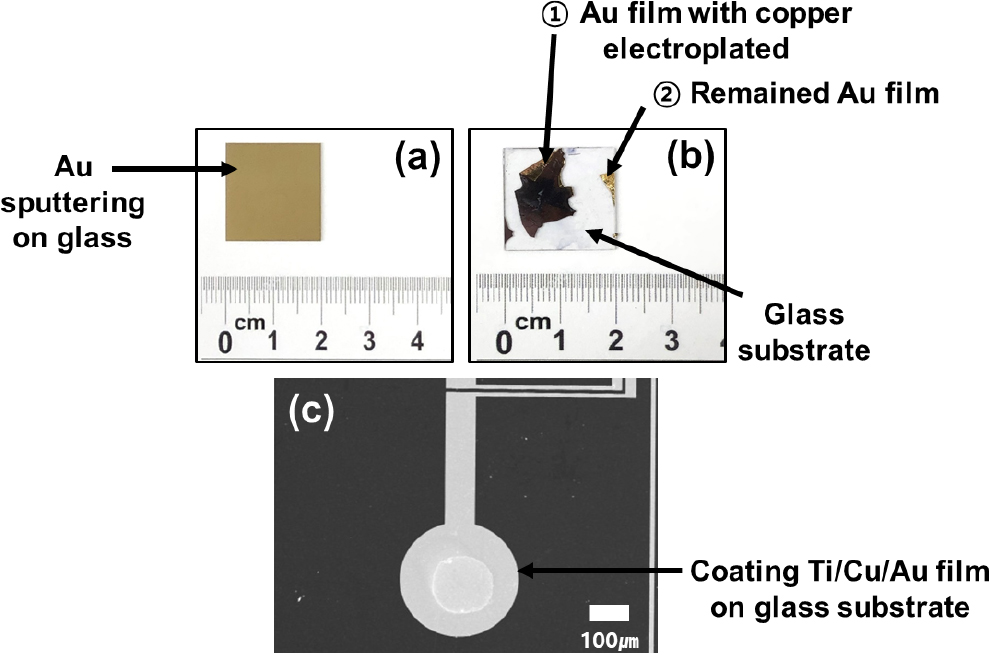

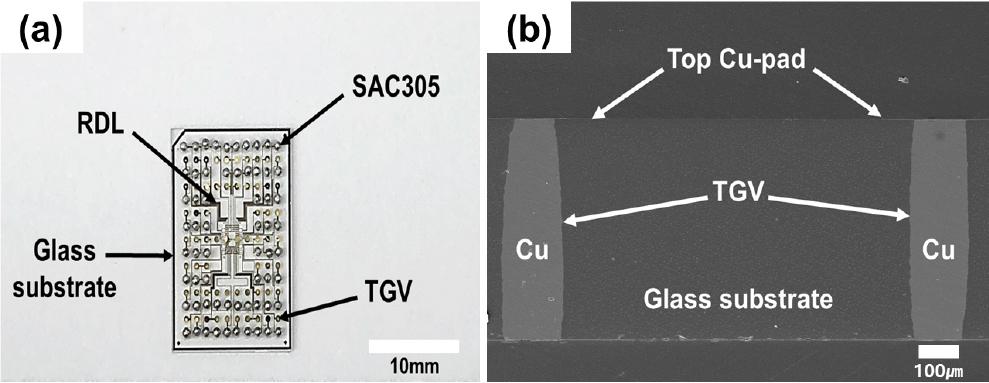

저자들은 유리 상에 금속 박막을 형성하기 위하여 Fig. 4와 같이 2 × 2 × 0.5 cm3 유리 기판 위에 접촉 저항(contact resistance)이 낮고, 화학적으로 안정한 비산화성 금속 중 하나인 Au를 20 mA로 9분 동안 Fig. 4(a)와 같이 스퍼터링하였다. 이후 전기도금법으로 Au 박막 위에 Cu를 전착하여 경과를 관찰하였다. 본 실험을 통해 Fig. 4(b)와 같이 전류를 인가했을 시 도금액 속에서 유리 상에 형성된 Au/Cu 박막이 함께 박리되는 현상(peel off)을 관찰할 수 있었다. 그러나, 유리와 금속층 사이에 접합력을 향상시키는 역할의 Ti를 코팅 시, Fig. 4(c)에 보인 것처럼 Cu층을 도금해도 박리 현상이 발생하지 않는 양호한 상태를 확인하였다.

또한 저자들은 TGV가 형성된 유리 기판 위에 범프를 형성하기 위한 실험을 행하였다. 실험을 위해 사용된 솔더볼은 Sn-3.0Ag-0.5Cu이고, 지름은 760 µm이다. 준비된 직경 600 µm Cu pad 위에 rosin mildly activated (RMA) 플럭스를 도포하고, 솔더볼을 마운팅하였다. Fig. 5(a)는 최대 온도 230 °C에서 90초 동안 대기중에서 리플로우하여 유리 기판 위에 솔더볼을 범핑한 결과이다. 이후 전단강도실험을 통해 측정된 TGV와 솔더 범프의 접합부의 전단강도는 약 3.63 MPa이었다.

5. 결 론

본 고에서는 AI 반도체를 위한 패키징과 TGV 기술의 최근 동향을 조사하였다. 휨 현상 없는 고품질의 TGV를 형성하기 위해서 필요한 적절한 유리 소재의 선택과 유리와 금속의 접합 신뢰성에 관한 최근 연구들에 대해 서술하였다. 유리 소재가 가진 낮은 유전 상수와 높은 절연 저항 등의 여러 장점으로 인해, 기존 실리콘 웨이퍼를 사용한 패키징 기술의 한계를 보완하는 데 중요한 역할을 할 수 있음을 시사하고 있다. 또한, 저자들이 실험한 TGV가 형성된 유리 기판의 Cu pad 상에 솔더볼을 접합한 사례도 소개하였다. 최근에는 artificial super intelligence (ASI)나 ChatGPT와 같이 인공지능 기술이 급속도로 발전하는 경향을 보이면서 기존 패키징 기술의 한계를 극복하기 위해 하이브리드 본딩, 3D 패키징과 함께 TGV 기술이 주목 받으면서 이와 관련된 많은 연구가 진행되고 있다. 금후 유리 기판에 적합한 비아 형성이나 비아 내 Cu 충전 기술의 최적화를 고려하는 방향으로 연구가 진행될 필요성도 있을 것으로 사료된다. AI와 TGV 기술의 발전을 통해 차세대 인공지능 반도체 패키징 분야의 더 나은 발전을 기대한다.