1. 서 론

유한한 연료 자원과 화석 연료 소비의 부정적인 환경적, 사회적 영향으로 인해 전기 자동차(EV) 기술 개발이 필수적으로 요구되고 있다.1) 공간이 제한된 전기 자동차에서 빠르고 효율적인 충전을 위해서는 높은 전력 밀도와 변환 효율이 필수적이다. 현재 전력 모듈 소자의 대부분을 ‘실리콘(Si)’ 기반으로 사용하고 있으나 Si 소자가 본질적인 한계에 도달함에 따라 열적인 문제와 빈번한 전류 스파이크 과전류와 같은 동작 환경에서 특성 저하의 위험이 있어 추가 설비를 해야 하는 단점이 있다.

Silicon carbide (SiC)는 ~3.3 eV의 넓은 밴드갭을 갖는 고에너지갭 반도체(WBG) 물질로 고내압, 저손실 전력 반도체용 소재로 유용하게 사용될 수 있고, Si 보다 약 10배 더 큰 ~3 MV/cm의 임계 전계를 갖는 화합물 반도체로서 전력 반도체 시장에서 주목받고 있는 소재이다. 또한 낮은 온저항 및 높은 항복전압으로 인해 전류 및 전압 전환 간격을 단축할 수 있어 스위칭 손실을 줄일 수 있다.2)

4H-SiC 소자의 상용화 과정에서 나타나는 다양한 결함들은 주요 장애물로 작용하고 있으며, 이 중 deep level trap과 관련된 연구는 소자 성능 향상을 위해 필수적이라 할 수 있다. 반도체 내부의 깊은 준위 결함은 캐리어가 결함에 트래핑 되는 현상과 캐리어 수명 단축을 초래함으로써, 누설 전류 증가와 같은 소자에 심각한 영향을 미치는 원인이 된다. 이에 따라, 4H-SiC 소자의 성능 개선을 위한 연구개발의 필요성이 더욱 강조되고 있다.3,4)

본 연구는 4H-SiC PiN diode의 전기적 특성과 깊은 준위 결함을 분석하였고, 시뮬레이션을 통해 깊은 준위 결함이 소자의 순방향 전압-전류 특성에 미치는 영향을 확인하였다.

2. 실험 방법

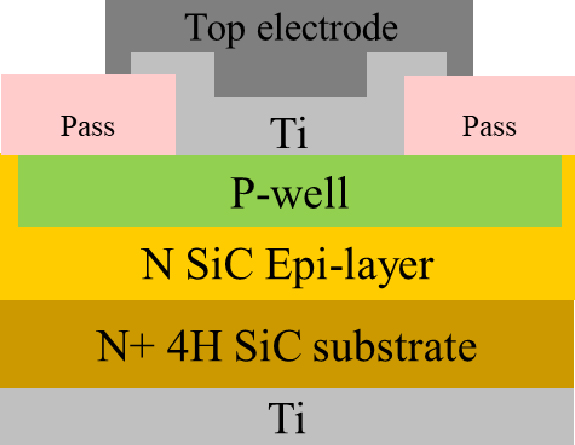

본 연구에서 사용된 소자는 4H-SiC 기반 PiN 다이오드이며 구조 및 파라메터는 Fig. 1과 Table 1에 정리하였다. 위 소자의 전기적 특성과 깊은 준위 결함을 분석하였으며 I-V, 1/C2-V curve를 통해 이상계수, on/off ratio, 누설전류를 도출할 수 있었다. 또한 deep level transient spectroscopy (DLTS)를 통해 소자의 에너지 준위(EC-ET), 포획 단면(σn), trap 밀도(nT)를 추출하여 분석하였다. 추출한 trap 파라메터를 2D-TCAD 시뮬레이션을 통해 설계한 4H-SiC PiN 다이오드 구조에 적용하여 캐리어 trapping에 의한 온저항과 이상계수의 증가와 같은 순방향특성의 저하를 확인했다.3,4)

Fig. 1은 설계 후 제작한 4H-SiC PiN 다이오드의 구조를 나타내고 있다. 구조에 따른 파라메터는 Table 1에 표기된 것과 같이 N타입 4H-SiC 에피층의 도핑농도는 1 × 1016 cm-3, 두께는 10 µm로 성장시켰다. Al implantation을 통해 0.5 µm의 두께와 1 × 1018 cm-3의 도핑농도로 P-well을 형성하였다. 양극과 음극의 오믹 접합은 모두 titanium (Ti)으로 형성하였고, active area는 1,462 × 1,462 µm2이다.

3. 결과 및 고찰

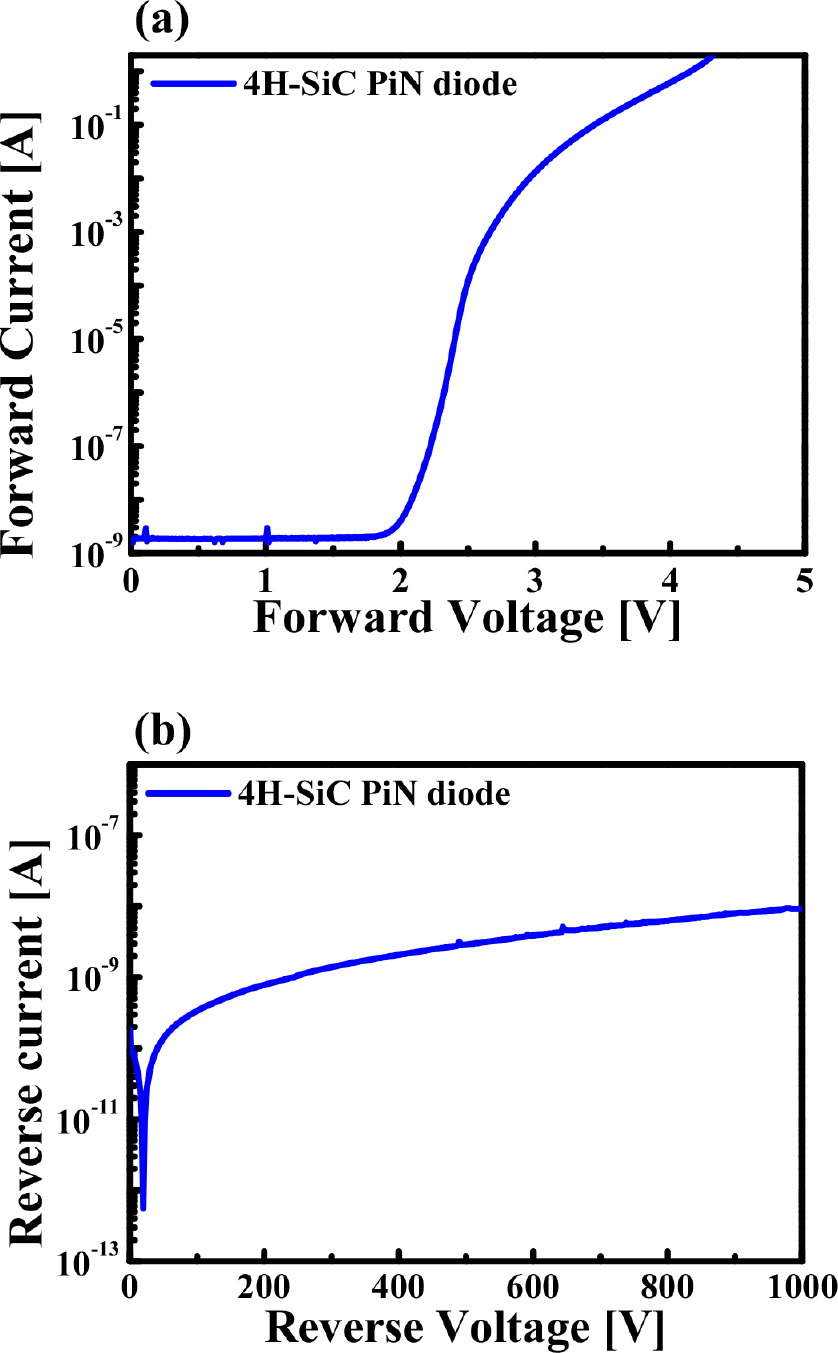

Fig. 2(a, b)는 4H-SiC PiN 다이오드의 대전압, 대전류 그래프이다. 제작한 소자의 Vth는 2.07 V이며, -10 V와 3 V에서 계산된 1.7 × 1010의 on/off ratio를 갖는다. 누설 전류의 경우 -10 V에서는 5.3 × 10-11 A, -1,000 V에서는 1 × 10-8 A의 낮은 누설전류를 보여준다. 이상계수의 경우 1.31로 계산되었으며, 위의 도출한 파라메터들은 Table 2에 정리되어 있다.

Table 2.

Electrical characteristics of 4H-SiC PiN diode.

| Parameters | Value |

| On/off ratio | 1.7 × 1010 |

| Built-in voltage (Vbi) [V] | 2.21 |

| Ideality factor (n) | 1.31 |

Fig. 3(a, b)는 50 kHz의 주파수에서 -9~0 V의 전압범위로 측정한 4H-SiC PiN 다이오드의 C-V, 1/C2-V 그래프이다. Fig. 3(b)의 그래프의 X축 절편으로 built-in voltage를 알 수 있으며 그 값은 2.21 V이다. I-V, C-V 측정결과를 통해 소자가 50 kHz의 주파수에서 온도 변화에 따른 DLTS 분석을 진행하기에 신뢰할 수 있는 다이오드 특성을 나타냈다.

Fig. 4(a)는 80~700 K의 온도범위에서 -9~0 V의 전압 범위와 50 kHz의 주파수, 100 mV의 frequency amplitude로 capacitance 변화를 측정하여 도출된 DLTS spectra이다. DLTS spectra를 통해 총 4개의 peak를 확인할 수 있었으며, 각 peak에 따른 trap 밀도는 람다보정이 포함된 식 (1)을 통해 도출되었다.5,6)

여기서, Cr은 역방향 전압(Vr = -9 V)에서의 접합 캐패시턴스, ΔC는 rate window (t2-t1)에 따른 depletion capacitance 차이이다. Trap 밀도는 Table 3에 정리했다.

Table 3.

Summary of trap information.

Fig. 4(b)는 DLTS spectra의 각 peak에서 추출한 Arrhenius plot 그래프를 보여준다. 위 그래프에서 포획 단면과 에너지 준위의 추출은 전자가 깊은 준위 결함에 포획되고, 다시 방출되는 과정에 따른 emission rate를 통해 계산할 수 있으며, 식 (2), (3)과 같이 나타낼 수 있다.7,8)

여기서, en은 emission rate, σn은 포획 단면, β는 유효질량과 같은 온도 비의존성 상수와 연관된 지수이다. 또한 Arrhenius plot에서 포획 단면과 에너지 준위는 각 trap에 해당하는 점들을 이은 직선의 기울기와 Y절편을 통해 추출할 수 있다. 이렇게 추출된 trap 파라메터들은 Table 3에 정리되어 있다.

DLTS spectra와 Arrhenius plot을 통해 추출된 trap 파라메터를 통해 각 trap이 생기는 원인에 대해 유추할 수 있다. P1 trap의 경우 DLTS spectra의 약 160 K 근처에서 나타나는 peak로 EC-ET는 0.282 eV이며, Al implantation에 의한 SH1* trap (0.2~0.26 eV)으로 유추할 수 있다.9) 이 trap은 implantation중 소수 캐리어 주입과 관련이 있으며, single plane stacking fault에 의해 나타난다.10,11) P2 trap은 DLTS spectra의 약 300 K에서 나타나며 EC-ET는 0.606 eV이다. 이 trap은 SiC의 주된 결함인 Z1/2로 유추할 수 있으며, carbon vacancy에 의해 나타나게 된다. Z1/2는 탄소 또는 Al등의 implantation후 annealing이나 고온 annealing을 통해 제거될 수 있으며, carbon vacancy에 기인하는 trap의 경우 소자의 캐리어 재결합 속도 감소에 큰 영향을 미치기 때문에 Z1/2 trap의 density를 줄이는 연구가 많이 진행되고 있다.12,13,14,15) P3 trap은 DLTS spectra의 385 K 근처에서 나타나며, EC-ET는 0.874 eV이다. 이 trap은 고에너지 implantation혹은 중성자 조사에 의해 발생하는 vacancy pair (VSi-VC)로 인한 RD1/2 trap (0.89~0.97 eV)로 유추할 수 있다.16,17) P4 trap의 경우 DLTS spectra의 610 K 근처에서 나타나며, EC-ET는 1.313 eV이다. 이 trap 또한 carbon vacancy에 기인하는 SiC의 주요 결함이며, 캐리어 수명을 감소시키고, SiC 기반 LED 등에서 발광효율을 감소시키는 결함이다.18,19)

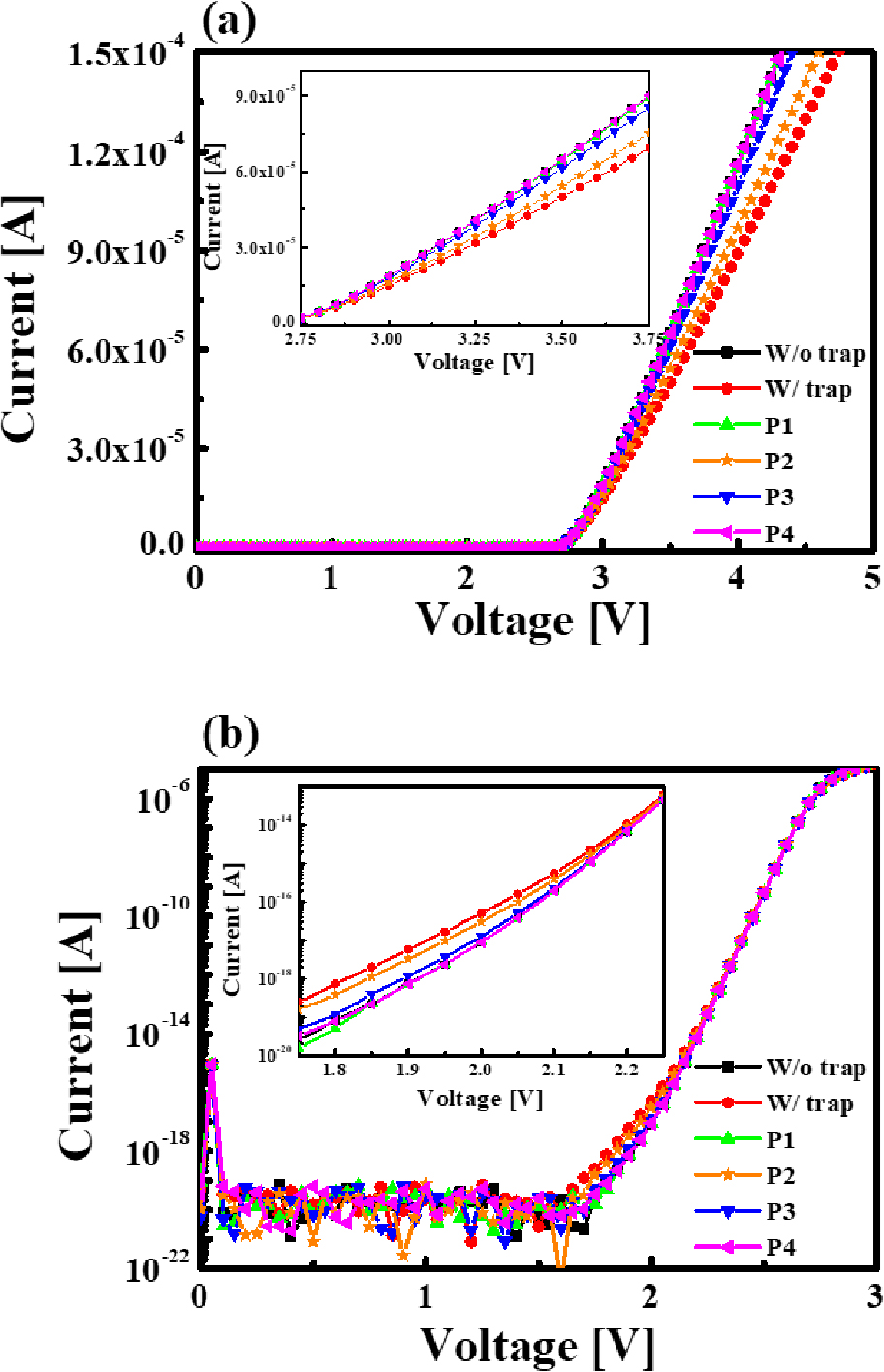

Fig. 5는 trap이 소자특성에 미치는 영향을 확인하기 위해 시뮬레이션을 통해 제작한 다이오드에 Fig. 4를 통해 추출한 trap 파라메터를 각각 또는 모두 적용하여 전압-전류특성을 확인한 그래프이다. 소자 시뮬레이션은 Silvaco사의 2D-TCAD simulator Atlas를 사용하였으며, 제작된 소자와 동일한 소자 구조를 적용하였다. Trap이 소자의 순방향 특성에 미치는 영향을 확인하기 위해 각 trap을 소자에 적용하여 전압-전류 특성을 시뮬레이션으로 확인하였다. Fig. 5(a)에서 trap으로 인해 순방향 바이어스에서 전류 레벨이 감소하며, 온저항이 증가하는 경향을 확인할 수 있었다. 특히 Z1/2를 의미하는 P2 trap이 전기적 특성에 가장 많은 영향을 미치며, 이는 Z1/2가 double acceptor-type deep level로, 전자를 포획하여 파워 디바이스의 온 상태 전압 강하를 일으키기 때문이다.19,20,21,22)Fig. 5(b)를 통해 볼 수 있듯이, trap을 추가함에 따라 기울기가 감소하며, 이는 이상계수의 증가를 뜻한다.13,23,24)

4. 결 론

본 논문에서는 4H-SiC PiN 다이오드의 전기적 특성과 깊은 준위 결함을 분석하고, 시뮬레이션을 통해 이러한 결함이 소자의 전기적 특성에 미치는 영향을 분석하였다. I-V 및 1/C2-V 곡선 분석을 통해 이상계수, built in voltage 등을 도출하였다. DLTS 분석을 통해 energy level과 trap 밀도 등을 추출할 수 있었고, 총 네가지 결함을 확인할 수 있었으며, SiC의 고유 결함인 P2, P4 (Z1/2, EH6/7)과 공정에 의해 생성되는 결함인 P1, P3 (SH1*, RD1/2)를 관찰할 수 있었다. 추출한 데이터를 바탕으로 2D-TCAD 시뮬레이션을 통해 설계한 4H-SiC PiN 다이오드 구조에 각 trap 파라메터를 적용하여 그에 따른 순방향 전압-전류 특성을 확인함으로써 trap으로 인한 온저항과 이상계수의 감소와 같은 부정적인 영향을 입증할 수 있었다. 본 연구는 SiC 소자의 결함 분석과 소자 성능 최적화 연계 특성에 대한 기반 연구를 수행하였다.